Question: 3) Assume a program executes 106 (1 million) instructions. 25% of instructions are load- store. The miss rate of the instruction cache is 4%

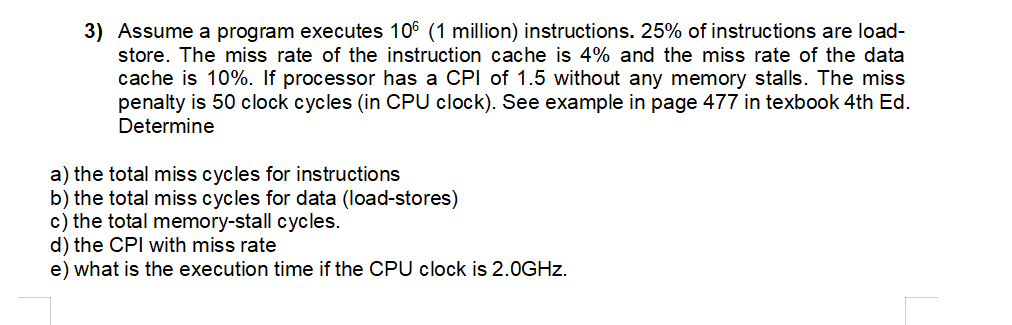

3) Assume a program executes 106 (1 million) instructions. 25% of instructions are load- store. The miss rate of the instruction cache is 4% and the miss rate of the data cache is 10%. If processor has a CPI of 1.5 without any memory stalls. The miss penalty is 50 clock cycles (in CPU clock). See example in page 477 in texbook 4th Ed. Determine a) the total miss cycles for instructions b) the total miss cycles for data (load-stores) c) the total memory-stall cycles. d) the CPI with miss rate e) what is the execution time if the CPU clock is 2.0GHz.

Step by Step Solution

There are 3 Steps involved in it

This question pertains to computer architecture specifically the impact of cache misses on the performance of a CPU executing a program Lets solve each part step by step a Total miss cycles for instru... View full answer

Get step-by-step solutions from verified subject matter experts