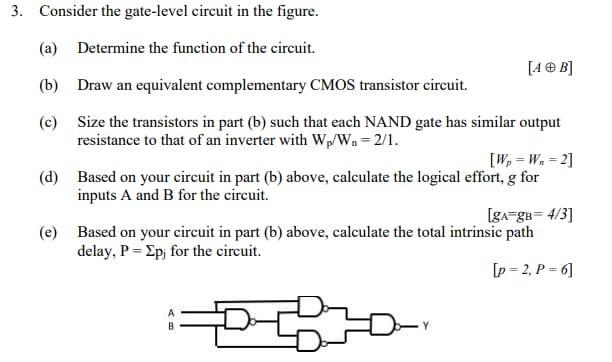

Question: 3. Consider the gate-level circuit in the figure. (a) Determine the function of the circuit. (b) Draw an equivalent complementary CMOS transistor circuit. [A

3. Consider the gate-level circuit in the figure. (a) Determine the function of the circuit. (b) Draw an equivalent complementary CMOS transistor circuit. [A B] (c) Size the transistors in part (b) such that each NAND gate has similar output resistance to that of an inverter with Wp/Wn=2/1. [W = WR = 2] (d) Based on your circuit in part (b) above, calculate the logical effort, g for inputs A and B for the circuit. [gA=gB=4/3] (e) Based on your circuit in part (b) above, calculate the total intrinsic path delay, P=p; for the circuit. Y [p=2, P=6]

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts