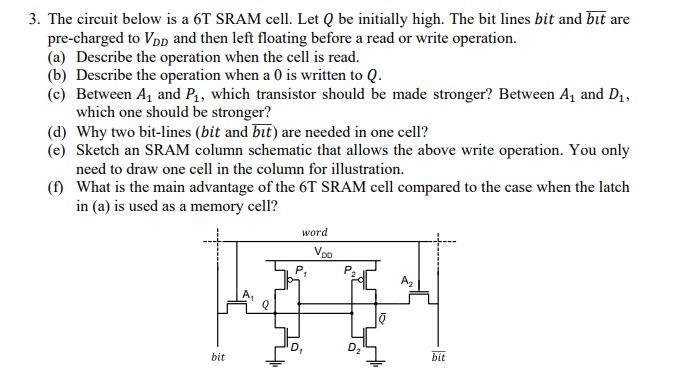

Question: 3 . The circuit below is a 6 T SRAM cell. Let ( Q ) be initially high. The bit lines bit and

The circuit below is a T SRAM cell. Let Q be initially high. The bit lines bit and overlineb i t are precharged to VD D and then left floating before a read or write operation.

a Describe the operation when the cell is read.

b Describe the operation when a is written to Q

c Between A and P which transistor should be made stronger? Between A and D which one should be stronger?

d Why two bitlines bit and overlineb i t are needed in one cell?

e Sketch an SRAM column schematic that allows the above write operation. You only need to draw one cell in the column for illustration.

f What is the main advantage of the T SRAM cell compared to the case when the latch in a is used as a memory cell?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock