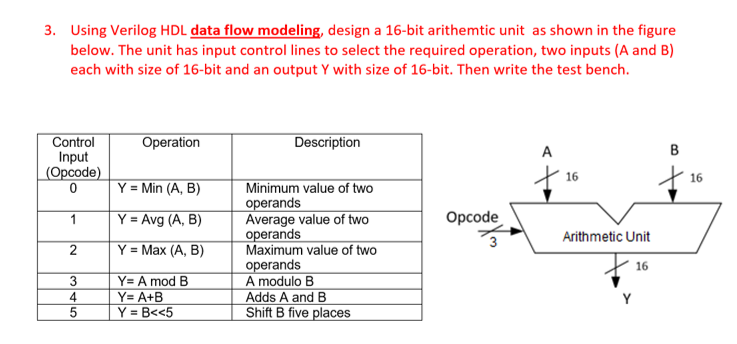

Question: 3. Using Verilog HDL data flow modeling, design a 16-bit arithemtic unit as shown in the figure below. The unit has input control lines to

3. Using Verilog HDL data flow modeling, design a 16-bit arithemtic unit as shown in the figure below. The unit has input control lines to select the required operation, two inputs (A and B) each with size of 16-bit and an output Y with size of 16-bit. Then write the test bench. Operation Description A B Control Input (Opcode) 0 16 16 Y = Min (A,B) 1 Y = Avg (A,B) Opcode Arithmetic Unit 2 Y = Max (A,B) Minimum value of two operands Average value of two operands Maximum value of two operands A modulo B Adds A and B Shift B five places 16 3 4 5 Y= A mod B Y=A+B Y = B

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts