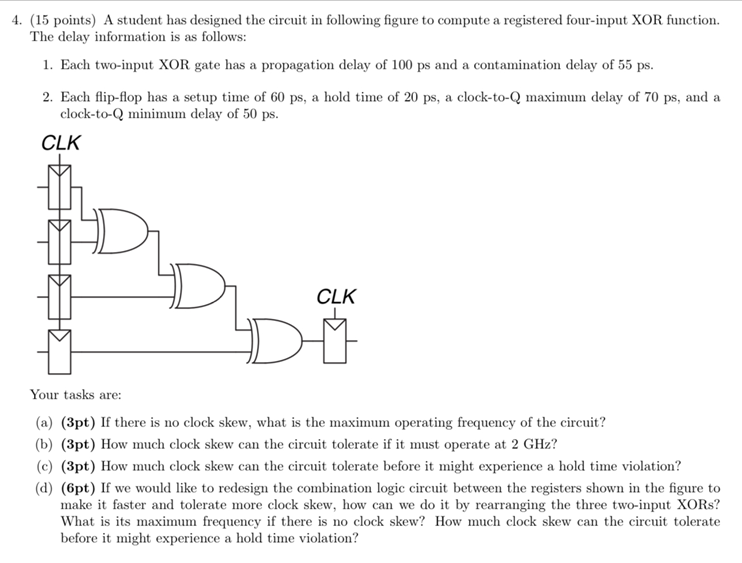

Question: 4 . ( 1 5 points ) A student has designed the circuit in following figure to compute a registered four - input XOR function.

points A student has designed the circuit in following figure to compute a registered fourinput XOR function. The delay information is as follows:

Each twoinput XOR gate has a propagation delay of ps and a contamination delay of ps

Each flipflop has a setup time of ps a hold time of ps a clocktoQ maximum delay of ps and a clocktoQ minimum delay of ps

Your tasks are:

apt If there is no clock skew, what is the maximum operating frequency of the circuit?

bpt How much clock skew can the circuit tolerate if it must operate at GHz

cpt How much clock skew can the circuit tolerate before it might experience a hold time violation?

dmathbfp t If we would like to redesign the combination logic circuit between the registers shown in the figure to make it faster and tolerate more clock skew, how can we do it by rearranging the three twoinput XORs? What is its maximum frequency if there is no clock skew? How much clock skew can the circuit tolerate before it might experience a hold time violation?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock