Question: 4. Cache performance The base CPI of a system, excluding memory stalls, is C Loads and stores collectively constitute LS% of all instructions Accessing the

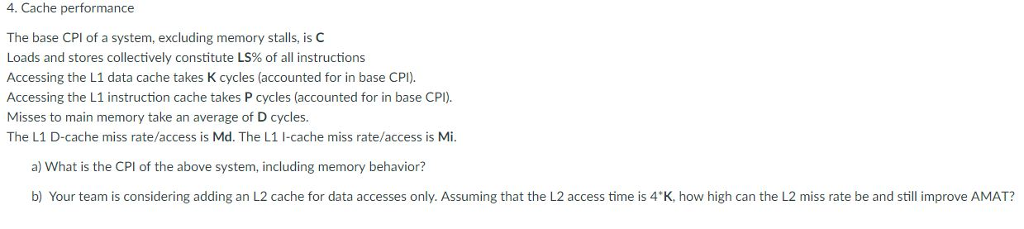

4. Cache performance The base CPI of a system, excluding memory stalls, is C Loads and stores collectively constitute LS% of all instructions Accessing the L1 data cache takes K cycles (accounted for in base CPl) Accessing the L1 instruction cache takes P cycles (accounted for in base CPI) Misses to main memory take an average of D cycles. The L1 D-cache miss rate/access is Md. The L1 I-cache miss rate/access is Mi. a) What is the CPl of the above system, including memory behavior? b) Your team is considering adding an L2 cache for data accesses only. Assuming that the L2 access time is 4"K, how high can the L2 miss rate be and still improve AMAT

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts