Question: 4 - Consider the following register - renamed code sequence executing on the microarchitecture shown below with the following assumptions: DADDI I S , R

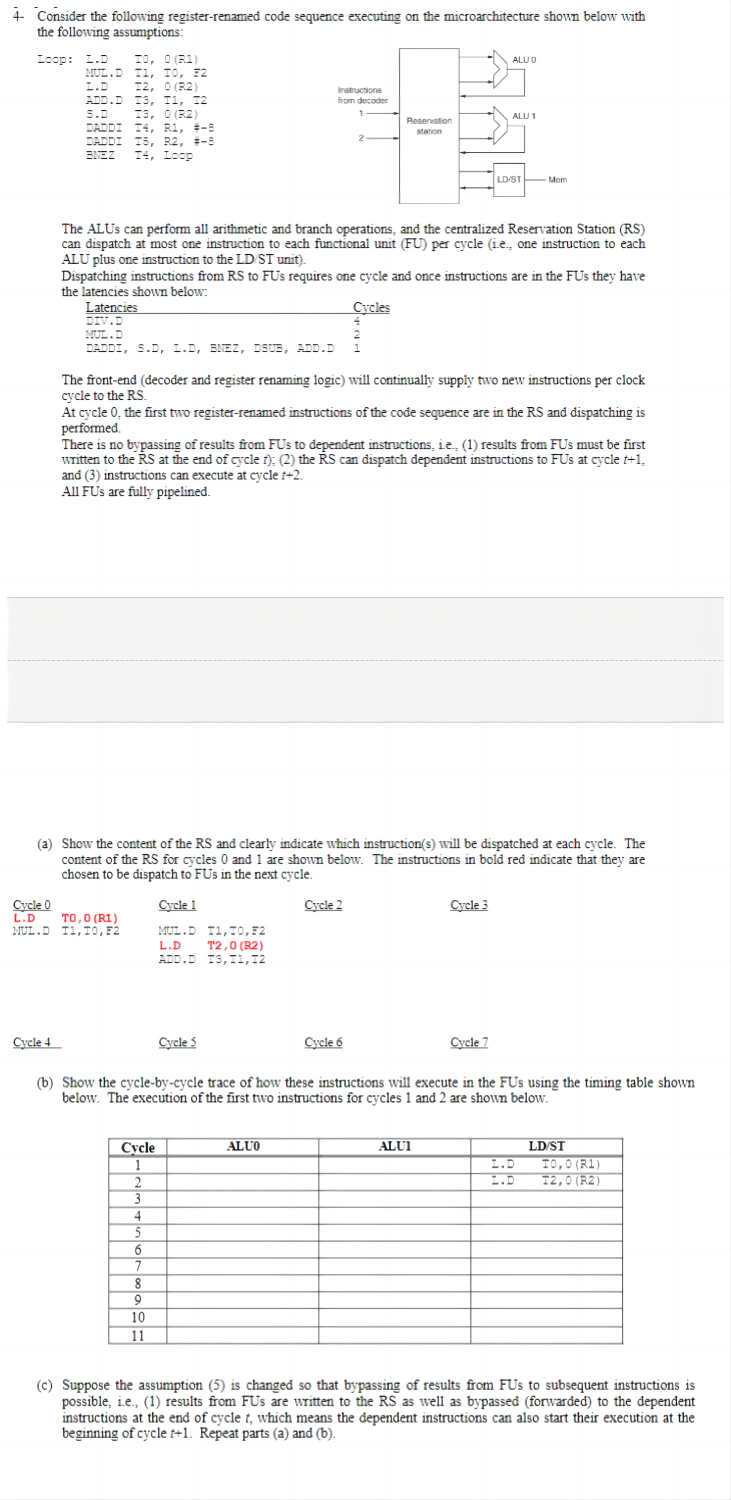

Consider the following registerrenamed code sequence executing on the microarchitecture shown below with

the following assumptions:

DADDI

BIEZ Iocp

The ALUs can perform all arithmetic and branch operations, and the centralized Reservation Station RS

can dispatch at most one instruction to each functional unit FU per cycle ie one instruction to each

ALU plus one instruction to the LD ST unit

Dispatching instructions from RS to FUs requires one cycle and once instructions are in the FUs they have

the latencies shown below:

The frontend decoder and register renaming logic will continually supply two new instructions per clock

cycle to the RS

At cycle the first two registerrenamed instructions of the code sequence are in the RS and dispatching is

performed.

There is no bypassing of results from FUs to dependent instructions, ie results from FUs must be first

written to the RS at the end of cycle ; the RS can dispatch dependent instructions to FUs at cycle

and instructions can execute at cycle

All FUs are fully pipelined.

a Show the content of the RS and clearly indicate which instructions will be dispatched at each cycle. The

content of the RS for cycles and are shown below. The instructions in bold red indicate that they are

chosen to be dispatch to FUs in the next cycle.

Cycle

Cycle

Cycle

Cycle

b Show the cyclebycycle trace of how these instructions will execute in the FUs using the timing table shown

below. The execution of the first two instructions for cycles and are shown below.

c Suppose the assumption is changed so that bypassing of results from FUs to subsequent instructions is

possible, ie results from FUs are written to the RS as well as bypassed forwarded to the dependent

instructions at the end of cycle which means the dependent instructions can also start their execution at the

beginning of cycle Repeat parts a and b

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock