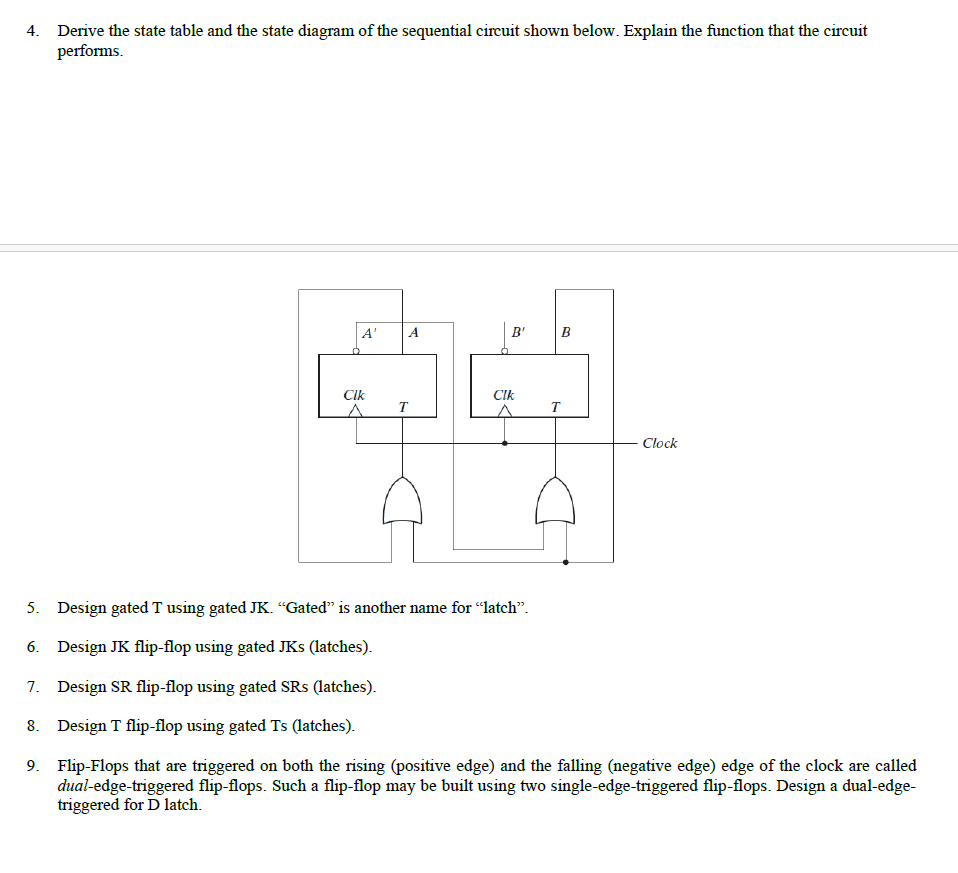

Question: 4 . Derive the state table and the state diagram of the sequential circuit shown below. Explain the function that the circuit performs. 5 .

Derive the state table and the state diagram of the sequential circuit shown below. Explain the function that the circuit performs.

Design gated T using gated JK "Gated" is another name for "latch".

Design JK flipflop using gated JKs latches

Design SR flipflop using gated SRs latches

Design T flipflop using gated Ts latches

FlipFlops that are triggered on both the rising positive edge and the falling negative edge edge of the clock are called dualedgetriggered flipflops. Such a flipflop may be built using two singleedgetriggered flipflops. Design a dualedge triggered for D latch.

can please help me answer questions to I don't need lengthy answers. something I can write as an answer to in an exam, with a little bit of explanation for computer science. I don't understand any mechanical, sophisticated terms.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock