Question: ( 5 0 pts ) Dynamic Logic Design Given ( mathrm { F } = mathrm { AB } + mathrm

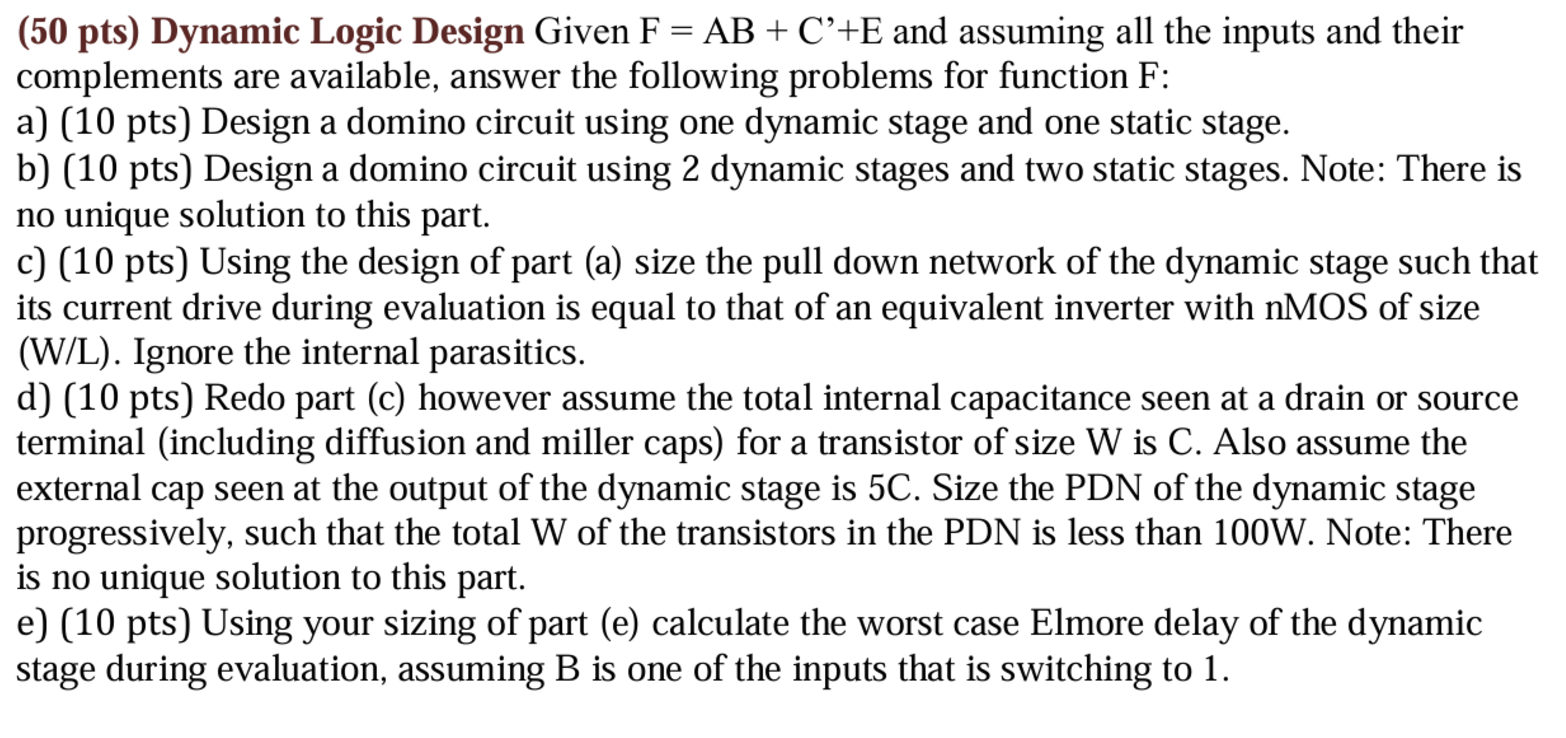

pts Dynamic Logic Design Given mathrmFmathrmABmathrmCprimemathrmE and assuming all the inputs and their complements are available, answer the following problems for function F :

a pts Design a domino circuit using one dynamic stage and one static stage.

b pts Design a domino circuit using dynamic stages and two static stages. Note: There is no unique solution to this part.

c pts Using the design of part a size the pull down network of the dynamic stage such that its current drive during evaluation is equal to that of an equivalent inverter with nMOS of size WL Ignore the internal parasitics.

d pts Redo part c however assume the total internal capacitance seen at a drain or source terminal including diffusion and miller caps for a transistor of size W is C Also assume the external cap seen at the output of the dynamic stage is C Size the PDN of the dynamic stage progressively, such that the total W of the transistors in the PDN is less than W Note: There is no unique solution to this part.

e pts Using your sizing of part e calculate the worst case Elmore delay of the dynamic stage during evaluation, assuming B is one of the inputs that is switching to

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock