Question: 5. Experiments with the ABC tool. ABC is a AIG-based synthesis and verification tool from Univ. California Berkeley. You find ABC as a NoMachine module;

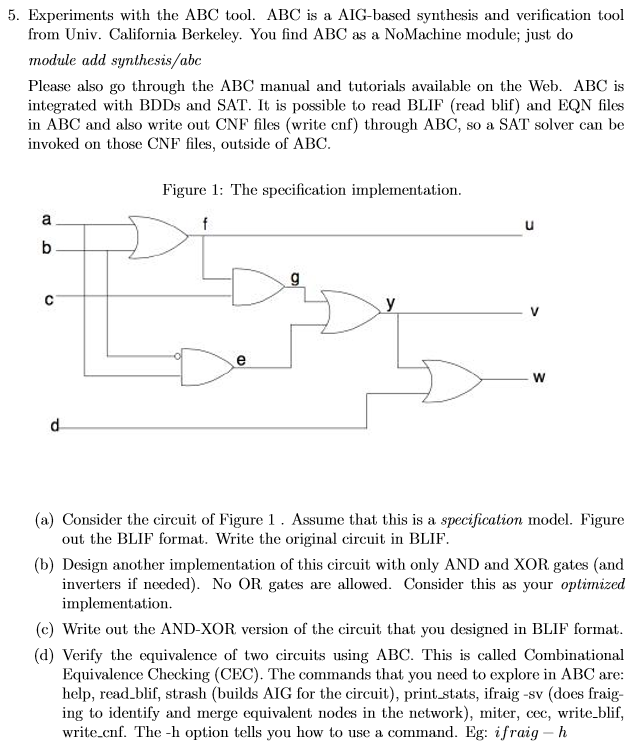

5. Experiments with the ABC tool. ABC is a AIG-based synthesis and verification tool from Univ. California Berkeley. You find ABC as a NoMachine module; just do module add synthesis/abc Please also go through the ABC manual and tutorials available on the Web. ABC is integrated with BDDs and SAT. It is possible to read BLIF (read blif) and EQN files in ABC and also write out CNF files (write cnf) through ABC, so a SAT solver can be invoked on those CNF files, outside of ABC Figure 1: The specification implementation (a) Consider the circuit of Figure 1. Assume that this is a specification model. Figure out the BLIF format. Write the original circuit in BLIF. (b) Design another implementation of this circuit with only AND and XOR gates (and inverters if needed). No OR gates are allowed. Consider this as your optimized implementation (c) Write out the AND-XOR version of the circuit that you designed in BLIF format (d) Verify the equivalence of two circuits using ABC. This is called Combinational Equivalence Checking (CEC). The commands that you need to explore in ABC are: help, read blif, strash (builds AIG for the circuit), print stats, ifraig -sv (does fraig ing to identify and merge equivalent nodes in the network), miter, cec, write.blif, write cnf. The -h option tells you how to use a command. Eg: ifraig -h 5. Experiments with the ABC tool. ABC is a AIG-based synthesis and verification tool from Univ. California Berkeley. You find ABC as a NoMachine module; just do module add synthesis/abc Please also go through the ABC manual and tutorials available on the Web. ABC is integrated with BDDs and SAT. It is possible to read BLIF (read blif) and EQN files in ABC and also write out CNF files (write cnf) through ABC, so a SAT solver can be invoked on those CNF files, outside of ABC Figure 1: The specification implementation (a) Consider the circuit of Figure 1. Assume that this is a specification model. Figure out the BLIF format. Write the original circuit in BLIF. (b) Design another implementation of this circuit with only AND and XOR gates (and inverters if needed). No OR gates are allowed. Consider this as your optimized implementation (c) Write out the AND-XOR version of the circuit that you designed in BLIF format (d) Verify the equivalence of two circuits using ABC. This is called Combinational Equivalence Checking (CEC). The commands that you need to explore in ABC are: help, read blif, strash (builds AIG for the circuit), print stats, ifraig -sv (does fraig ing to identify and merge equivalent nodes in the network), miter, cec, write.blif, write cnf. The -h option tells you how to use a command. Eg: ifraig -h

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts