Question: 5- Need help with EE/ compE question 5. [30 ptsl Design a sequence recognizer. In this problem you will be designing a sequential circuit for

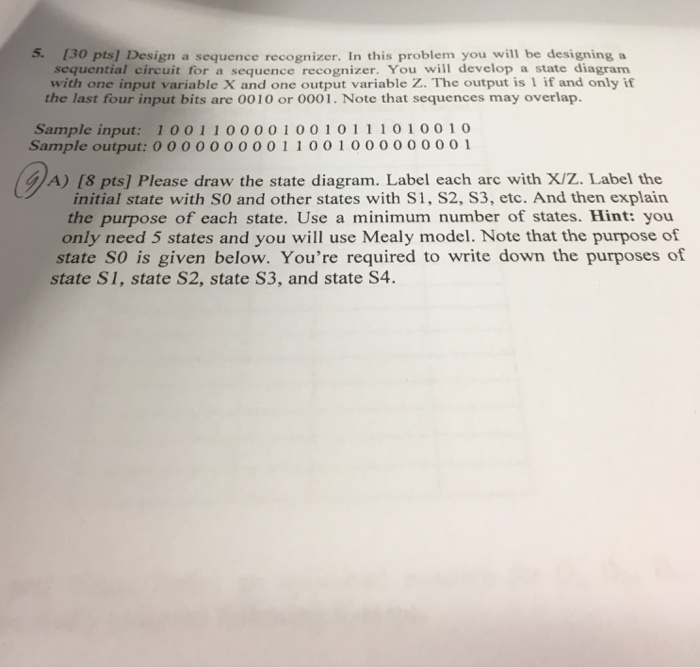

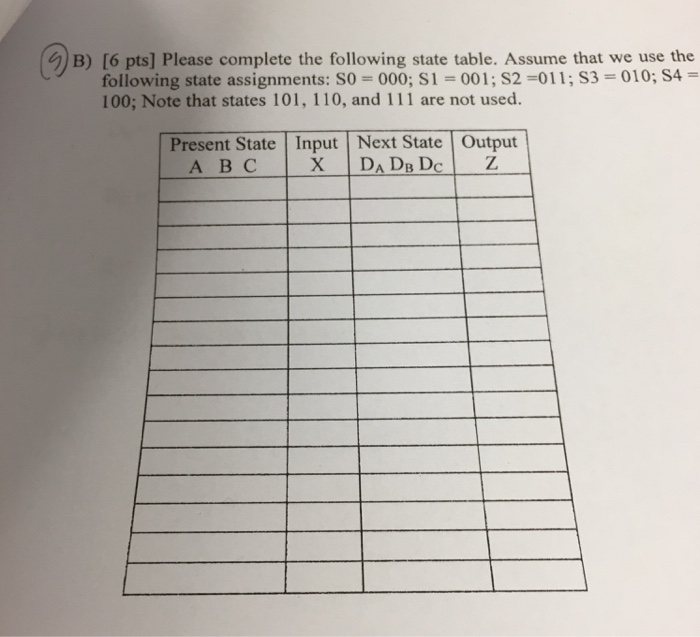

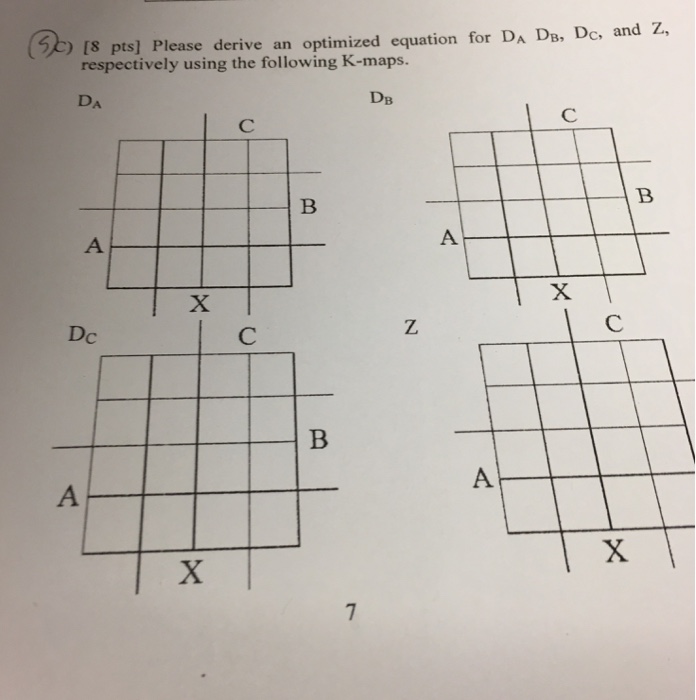

5. [30 ptsl Design a sequence recognizer. In this problem you will be designing a sequential circuit for a sequence recognizer. You will develop a state diagram with one input variable X and one output variable Z. The output is 1 if and only if the last four input bits are oo 10 or oo01. Note that sequences may overlap. Sample input. 1 0 0 1 1 0 0 0 0 1 0 0 1 01 1 100 1 00 10 Sample output: 0 0 0 0 0 0 0 0 0 1 10 o 1 0 0 0 0 0 01 A) 18 pts] Please draw the state diagram. Label each arc with xuZ. Label the initial state with so and other states with S1, S2, S3, etc. And then explain the purpose of each state. Use a minimum number of states. Hint: you only need 5 states and you will use Mealy model. Note that the purpose of state So is given below. You're required to write down the purposes of state S1, state S2, state S3, and state S4

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts