Question: 6. Register File Design (15 points) You are tasked with designing a register file for the CprE281 computer. The CprE281 has an 8 bit wide

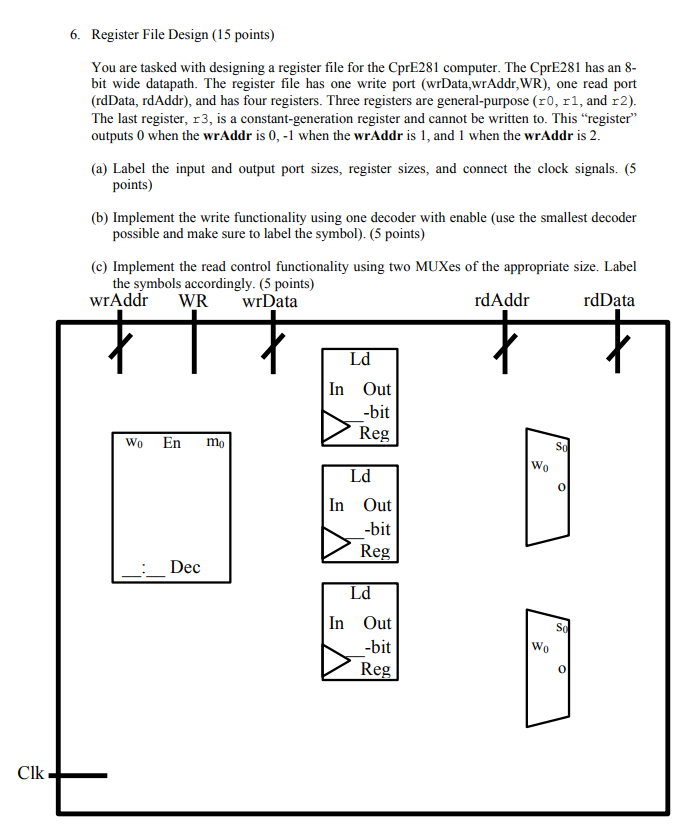

6. Register File Design (15 points) You are tasked with designing a register file for the CprE281 computer. The CprE281 has an 8 bit wide datapath. The register file has one write port (wrData, wrAddr,WR), one read port (rdData, rdAddr), and has four registers. Three registers are general-purpose (r0, r1, and r2). The last register, r3, is a constant-generation register and cannot be written to. This "register" outputs 0 when the wrAddr is 0, -1 when the wrAddr is 1, and 1 when the wrAddr is 2. (a) Label the input and output port sizes, register sizes, and connect the clock signals. (5 points) (b) Implement the write functionality using one decoder with enable (use the smallest decoder possible and make sure to label the symbol). (5 points) (c) Implement the read control functionality using two MUXes of the appropriate size. Label the symbols accordingly. (5 points) wrAddr WRwrData rdAddr rdData In Out -bit Reg Wo En o Ld 0 In Out it Reg Dec In Out it Reg 0 Clk 6. Register File Design (15 points) You are tasked with designing a register file for the CprE281 computer. The CprE281 has an 8 bit wide datapath. The register file has one write port (wrData, wrAddr,WR), one read port (rdData, rdAddr), and has four registers. Three registers are general-purpose (r0, r1, and r2). The last register, r3, is a constant-generation register and cannot be written to. This "register" outputs 0 when the wrAddr is 0, -1 when the wrAddr is 1, and 1 when the wrAddr is 2. (a) Label the input and output port sizes, register sizes, and connect the clock signals. (5 points) (b) Implement the write functionality using one decoder with enable (use the smallest decoder possible and make sure to label the symbol). (5 points) (c) Implement the read control functionality using two MUXes of the appropriate size. Label the symbols accordingly. (5 points) wrAddr WRwrData rdAddr rdData In Out -bit Reg Wo En o Ld 0 In Out it Reg Dec In Out it Reg 0 Clk

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts