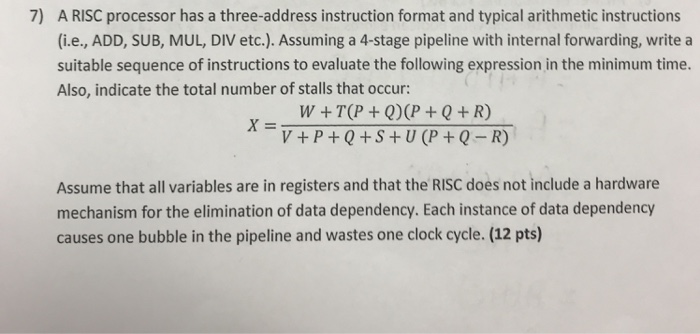

Question: 7) ARISC processor has a three-address instruction format and typical arithmetic instructions (i.e, ADD, SUB, MUL, DIV etc.). Assuming a 4-stage pipeline with internal forwarding,

7) ARISC processor has a three-address instruction format and typical arithmetic instructions (i.e, ADD, SUB, MUL, DIV etc.). Assuming a 4-stage pipeline with internal forwarding, write a suitable sequence of instructions to evaluate the following expression in the minimum time. Also, indicate the total number of stalls that occur: W +T(P+Q)(P Q+R) V+P +Q+S+UCP+Q-R) Assume that all variables are in registers and that the RISC does not include a hardware mechanism for the elimination of data dependency. Each instance of data dependency causes one bubble in the pipeline and wastes one clock cycle. (12 pts)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts