Question: [70] Consider the memory hierarchy depicted below where a TLB and data cache are shown 1. Virtual address 31 30 29 14 13 12 11

![[70] Consider the memory hierarchy depicted below where a TLB and](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f31ec19e1dc_15366f31ec12a100.jpg)

[70] Consider the memory hierarchy depicted below where a TLB and data cache are shown 1. Virtual address 31 30 29 14 13 12 11 10 93 2 1 Virtual page number Page offset 20 Valid Dirty Tag Physical page number TLB TLB hit 20 Physical page number Page offset ical address Byte offset Physical address tag Cache index offset 42 12 Data Valid Cache Cache hit 32 Data Note: the arrays don't show every entry. For example the TLB is 16 entries long You can think of the data cache as being comprised of lines (blocks) that have 16 sub- blocks of four bytes each. Not shown is a multiplexor that uses the block offset bits to select which sub-block will be delivered to the data outputs

Step by Step Solution

There are 3 Steps involved in it

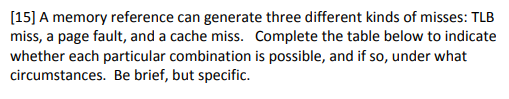

Get step-by-step solutions from verified subject matter experts