Question: please fast Question (1 Point) Consider executing the following MIPS instruction: LW Sto, 4(Ss0) Assume: Assume MIPS memory system with TLB and data cache Ss0

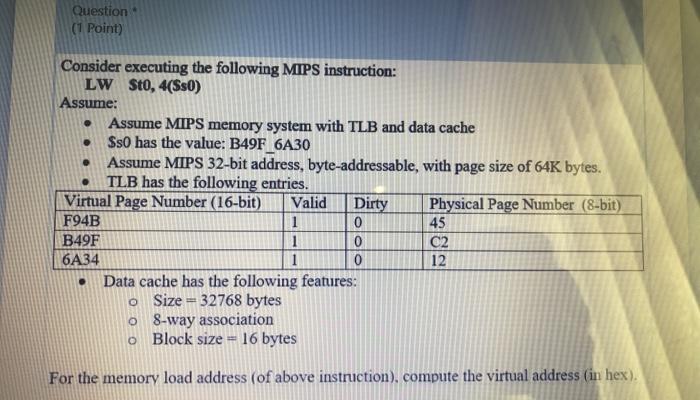

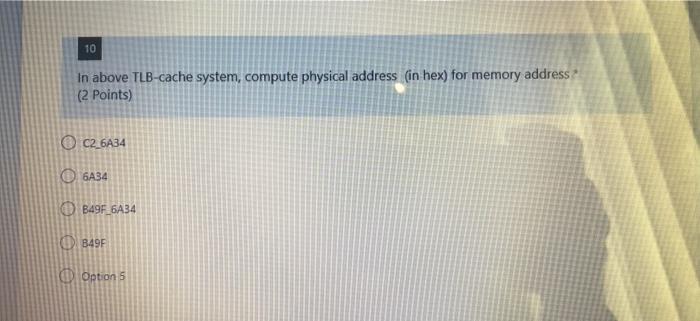

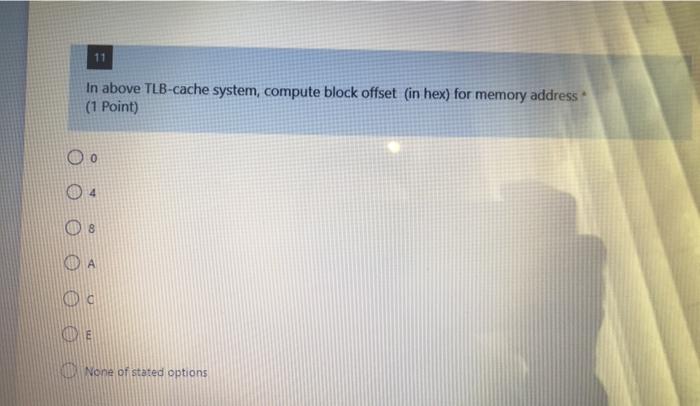

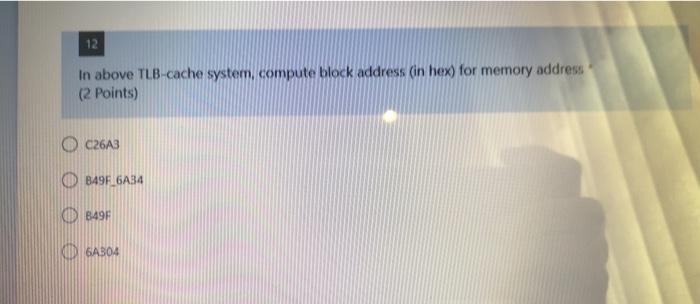

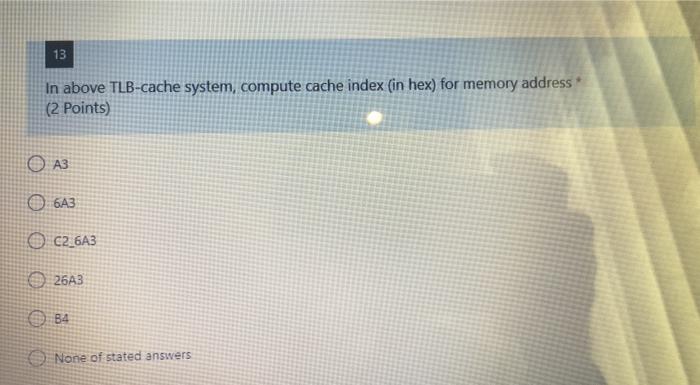

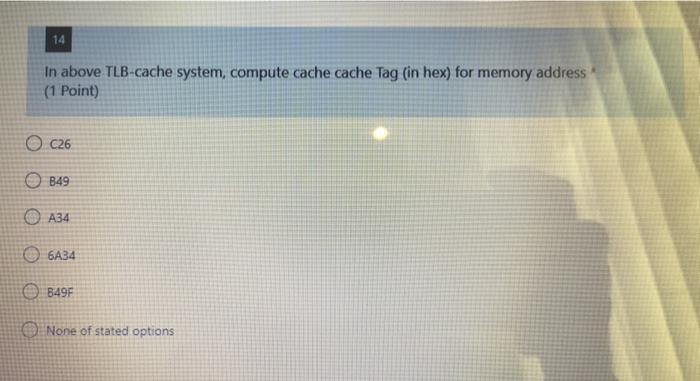

Question (1 Point) Consider executing the following MIPS instruction: LW Sto, 4(Ss0) Assume: Assume MIPS memory system with TLB and data cache Ss0 has the value: B49F_6A30 Assume MIPS 32-bit address, byte-addressable, with page size of 64K bytes. TLB has the following entries. Virtual Page Number (16-bit) Valid Dirty Physical Page Number (8-bit) F94B 1 0 45 B49F 1 0 C2 6A34 1 0 12 Data cache has the following features: o Size = 32768 bytes o 8-way association 0 Block size = 16 bytes . For the memory load address (of above instruction), compute the virtual address (in hex). 10 In above TLB-cache system, compute physical address (in hex) for memory address (2 points) Oc2_6A34 O 6134 1 B49F_6A34 849 Options 11 In above TLB-cache system, compute block offset (in hex) for memory address (1 Point) 0 DA DE None of stated options 12 In above TLB cache system, compute block address (in hex) for memory address (2 points) C26A3 B49F6A34 DB49F D6AB04 13 In above TLB-cache system, compute cache index (in hex) for memory address (2 Points) O 6A3 C2_6A3 26A3 O None of stated answers 14 In above TLB-cache system, compute cache cache Tag (in hex) for memory address (1 Point) O 026 B49 O A34 6A34 649 None of stated options

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts