Question: A 32-bit mainframe computer from 1975 had a high speed memory buffer implemented as a 2-way set-associative cache, organised as follows: - Capacity: 16KB -

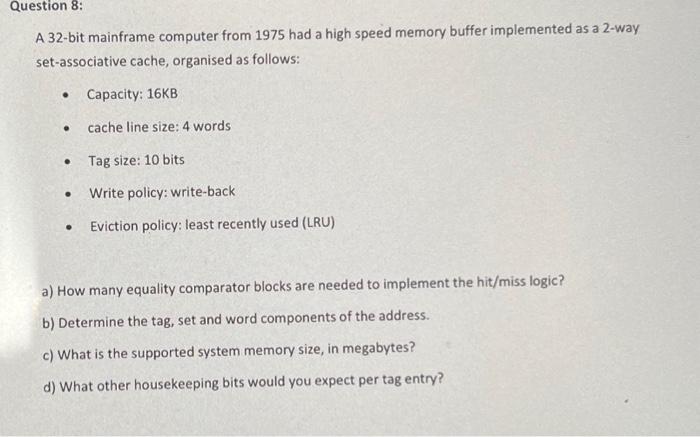

A 32-bit mainframe computer from 1975 had a high speed memory buffer implemented as a 2-way set-associative cache, organised as follows: - Capacity: 16KB - cache line size: 4 words - Tag size: 10 bits - Write policy: write-back - Eviction policy: least recently used (LRU) a) How many equality comparator blocks are needed to implement the hit/miss logic? b) Determine the tag, set and word components of the address. c) What is the supported system memory size, in megabytes? d) What other housekeeping bits would you expect per tag entry

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts