Question: A 32-bit mainframe computer from 1975 had an instruction unit implemented on a multilayer board with an array of 67 LSI chips, with each chip

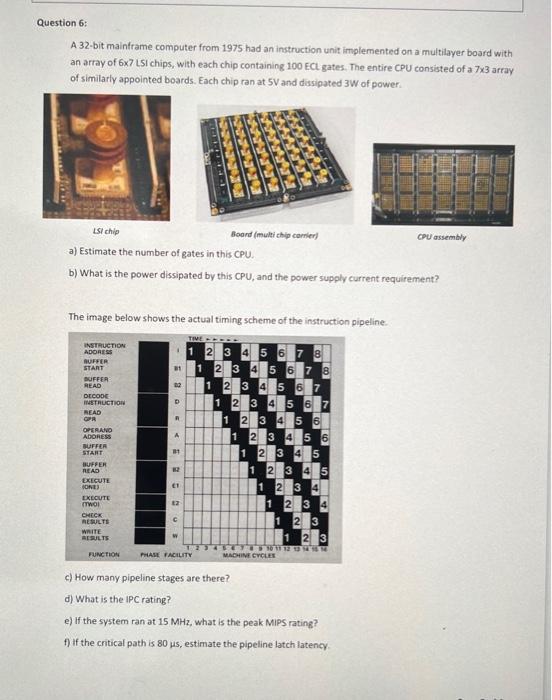

A 32-bit mainframe computer from 1975 had an instruction unit implemented on a multilayer board with an array of 67 LSI chips, with each chip containing 100ECl gates. The entire CPU consisted of a 73 array of similarly appointed boards. Each chip ran at 5V and dissipated 3W of power. 15/ chip a) Estimate the number of gates in this CPU. b) What is the power dissipated by this CPU, and the power supply current requirement? The image below shows the actual timing scheme of the instruction pipeline. c) How many pipeline stages are there? d) What is the IPC rating? e) If the system ran at 15MHz, what is the peak MiPS rating? f) If the critical path is 80 s, estimate the pipeline latch latency

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts