Question: A clock-mode sequential circuit receives data bits from the X-input in serial form, synchronously with the clock. This circuit evaluates the data bits in groups

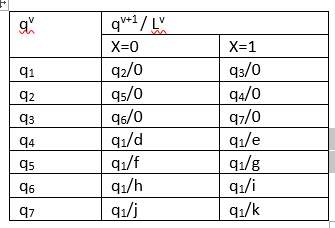

A clock-mode sequential circuit receives data bits from the X-input in serial form, synchronously with the clock. This circuit evaluates the data bits in groups of three to produce an L output as shown in the table below. State chart of the circuit is given below.

a) Construct the reduced state table by determining the identical cases.

b) At least how many flip-flops should be used to realize this circuit using D flip-flops? Determine. Construct the excitation diagrams for the least significant state variable.

ak 91 92 93 qV+1/L X=0 92/0 95/0 96/0 91/d 91/f 91/h qi/j X=1 93/0 44/0 97/0 91/e 1/8 91/1 91/ 44 95 96 q7 ak 91 92 93 qV+1/L X=0 92/0 95/0 96/0 91/d 91/f 91/h qi/j X=1 93/0 44/0 97/0 91/e 1/8 91/1 91/ 44 95 96 q7

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts