Question: A combinational logic circuit has a propagation delay of 10 ns and a contamination delay of 4 ns. Assume we are given the truth table

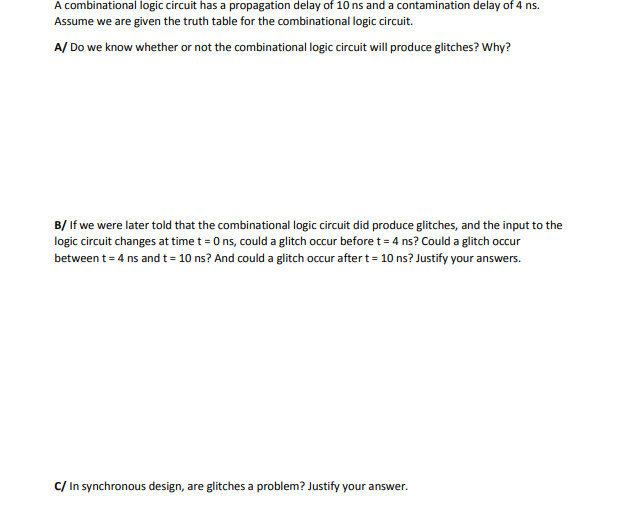

A combinational logic circuit has a propagation delay of 10 ns and a contamination delay of 4 ns. Assume we are given the truth table for the combinational logic circuit. A/ Do we know whether or not the combinational logic circuit will produce glitches? Why? B/ If we were later told that the combinational logic circuit did produce glitches, and the input to the logic circuit changes at time t = 0ns, could a glitch occur before t = 4 ns? Could a glitch occur between t = 4 ns and t = 10 ns? And could a glitch occur after t= 10 ns? Justify your answers. C/ In synchronous design, are glitches a problem? Justify your answer. A combinational logic circuit has a propagation delay of 10 ns and a contamination delay of 4 ns. Assume we are given the truth table for the combinational logic circuit. A/ Do we know whether or not the combinational logic circuit will produce glitches? Why? B/ If we were later told that the combinational logic circuit did produce glitches, and the input to the logic circuit changes at time t = 0ns, could a glitch occur before t = 4 ns? Could a glitch occur between t = 4 ns and t = 10 ns? And could a glitch occur after t= 10 ns? Justify your answers. C/ In synchronous design, are glitches a problem? Justify your

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts