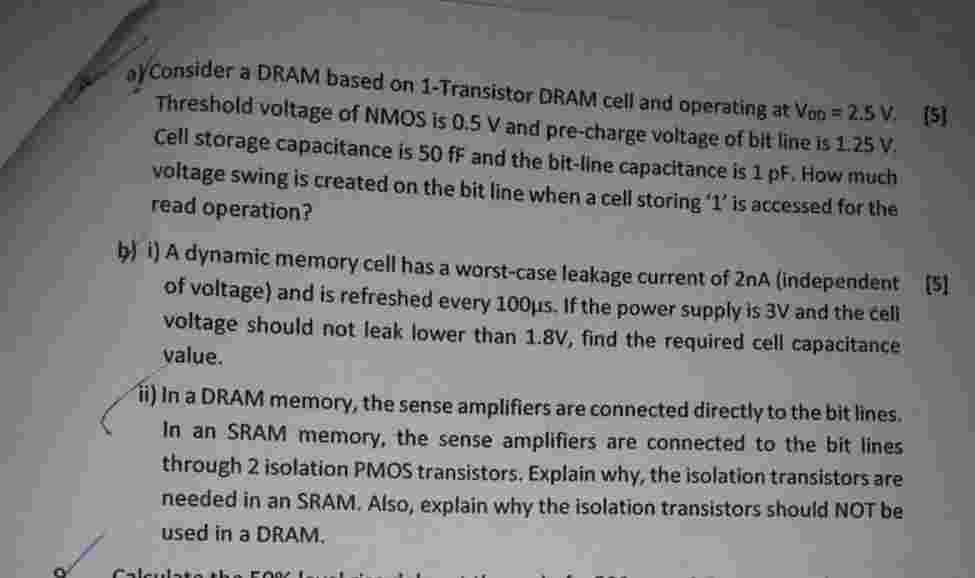

Question: a ) Consider a DRAM based on 1 - Transistor DRAM cell and operating at ( mathrm { V } _ {

a Consider a DRAM based on Transistor DRAM cell and operating at mathrmVmathrmODmathrm~V Threshold voltage of NMOS is V and precharge voltage of bit line is V

Cell storage capacitance is fF and the bitline capacitance is pF How much voltage swing is created on the bit line when a cell storing is accessed for the read operation?

b i A dynamic memory cell has a worstcase leakage current of nA independent of voltage and is refreshed every mu If the power supply is V and the cell

voltage should not leak lower than V find the required cell capacitance value.

ii In a DRAM memory, the sense amplifiers are connected directly to the bit lines. In an SRAM memory, the sense amplifiers are connected to the bit lines through isolation PMOS transistors. Explain why, the isolation transistors are needed in an SRAM. Also, explain why the isolation transistors should NOT be used in a DRAM.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock