Question: A CPU implements a stack-based i.e., zero-address) instruction set, where there are four general purpose resisters (RO, R1, R2, and R3), a stack pointer (SP),

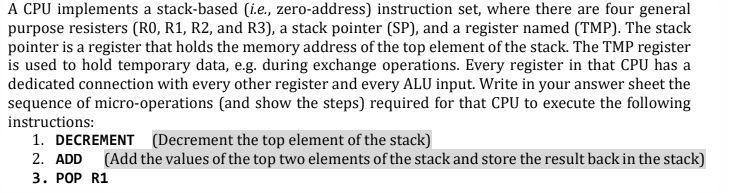

A CPU implements a stack-based i.e., zero-address) instruction set, where there are four general purpose resisters (RO, R1, R2, and R3), a stack pointer (SP), and a register named (TMP). The stack pointer is a register that holds the memory address of the top element of the stack. The TMP register is used to hold temporary data, e.g. during exchange operations. Every register in that CPU has a dedicated connection with every other register and every ALU input. Write in your answer sheet the sequence of micro-operations and show the steps) required for that CPU to execute the following instructions: 1. DECREMENT (Decrement the top element of the stack) 2. ADD (Add the values of the top two elements of the stack and store the result back in the stack) 3. POP R1

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts