Question: a) i) Design a logic circuit (using 2-input logic gates) of a 1-bit full adder that uses carry ripple logic. You also need to show

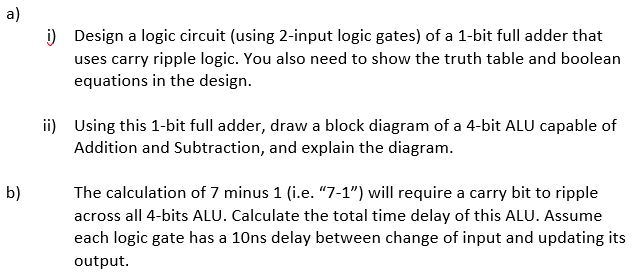

a) i) Design a logic circuit (using 2-input logic gates) of a 1-bit full adder that uses carry ripple logic. You also need to show the truth table and boolearn equations in the design i) Using this 1-bit full adder, draw a block diagram of a 4-bit ALU capable of Addition and Subtraction, and explain the diagram b) The calculation of 7 minus 1 (i.e. "7-1") will require a carry bit to ripple across all 4-bits ALU. Calculate the total time delay of this ALU. Assume each logic gate has a 10ns delay between change of input and updating its output

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts