Question: A micro-controller company has a single-cycle CPU model with a cycle time of 10ns. The company decides to turn the single-cycle CPU into a

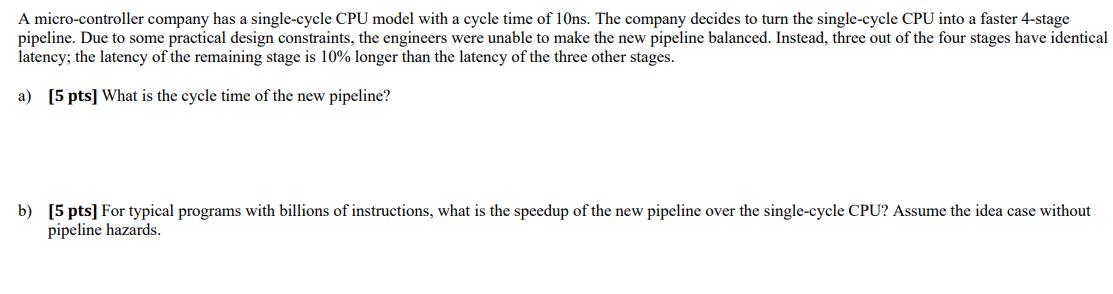

A micro-controller company has a single-cycle CPU model with a cycle time of 10ns. The company decides to turn the single-cycle CPU into a faster 4-stage pipeline. Due to some practical design constraints, the engineers were unable to make the new pipeline balanced. Instead, three out of the four stages have identical latency; the latency of the remaining stage is 10% longer than the latency of the three other stages. a) [5 pts] What is the cycle time of the new pipeline? b) [5 pts] For typical programs with billions of instructions, what is the speedup of the new pipeline over the single-cycle CPU? Assume the idea case without pipeline hazards.

Step by Step Solution

3.46 Rating (153 Votes )

There are 3 Steps involved in it

The provided image describes a scenario in which a microcontroller company has a singlecycle CPU model with a cycle time of 10ns and is transitioning ... View full answer

Get step-by-step solutions from verified subject matter experts