Question: A new processor design implements a 5 - stage pipeline ( Fetch , Decode, Execute, Memory, Writeback ) . Each stage performs its operation and

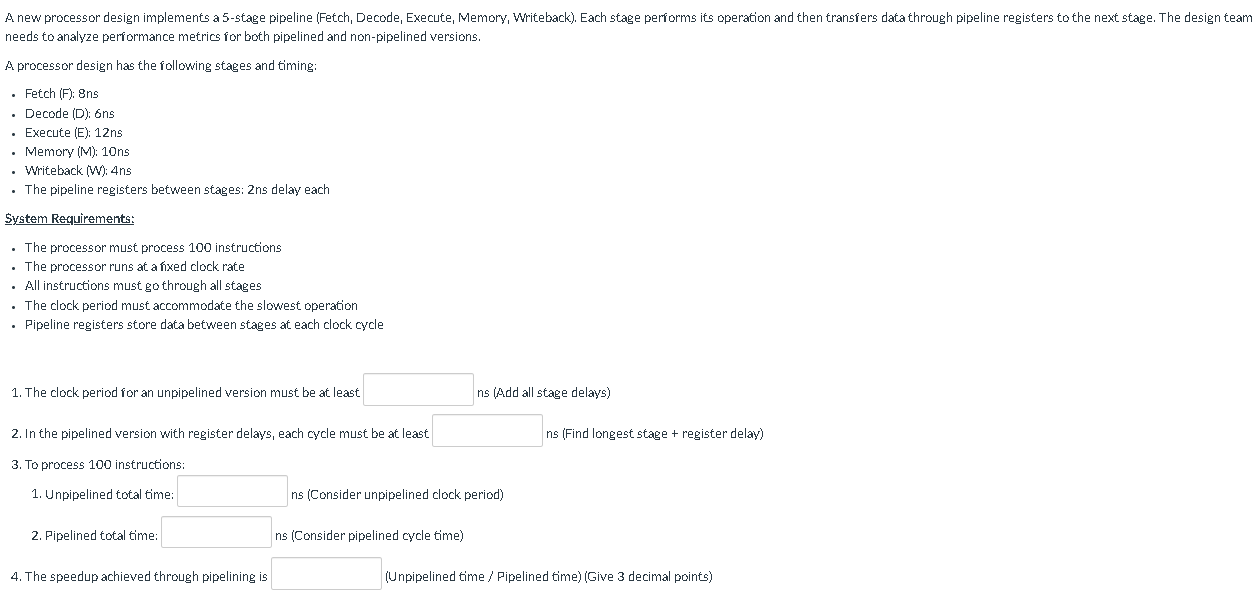

A new processor design implements a stage pipeline Fetch Decode, Execute, Memory, Writeback Each stage performs its operation and then transfers data through pipeline registers to the next stage. The design team needs to analyze performance metrics for both pipelined and nonpipelined versions.

A processor design has the following stages and timing:

Fetch F: Bns

Decode D: ns

Execute E: ns

Memory M; ns

Writeback W: ns

The pipeline registers between stages: ns delay each

system Requirements:

The processor must process instructions

The processor runs at a fixed clock rate

All instructions must go through all stages

The clock period must accommodate the slowest operation

Pipeline registers store data between stages at each clock cycle

The clock period for an unpipelined version must be at least ns Add all stage delays

In the pipelined version with register delays, each cycle must be at least

ns Find longest stage register delay

To process instructions:

Unpipelined total time: ns Consider unpipelined clock period

Pipelined total time: ns Consider pipelined cycle time

The speedup achieved through pipelining is

Unpipelined time Pipelined timeGive decimal points

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock