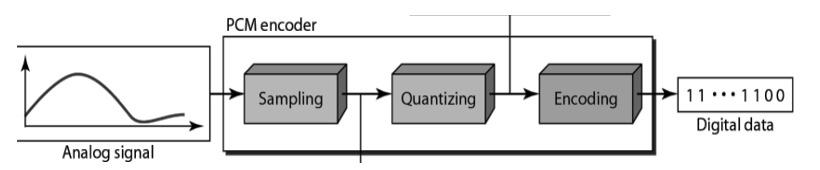

Question: A PCM encoder block diagram is shown below: The encoder at the output of the block diagram is a serial encoder which is generating the

A PCM encoder block diagram is shown below:

The encoder at the output of the block diagram is a serial encoder which is generating the output bits in series. The system has been designed for real time PCM encoding of the analog input signal. While generating the serial output bit stream, the system suddenly develops a strange fault. The rate of generation of the output bit steam starts to fluctuate. Obviously this would create a severe problem at the PCM decoder being used at the receiver since this receiver would not be able to reconstruct the analog signal being transmitted correctly.

- You are required to analyze the scenario and discuss what could be the reason/s for the fluctuation in the bit generation rate at the output of the PCM encoder and how this could be controlled.

b. Is it possible that the data at the receiver could still be retrieved correctly despite variation in the rate of generation of the bits at the transmitters output? Discuss

PCM encoder Sampling Quantizing Encoding 11 ... 1100 Digital data Analog signal PCM encoder Sampling Quantizing Encoding 11 ... 1100 Digital data Analog signal

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts