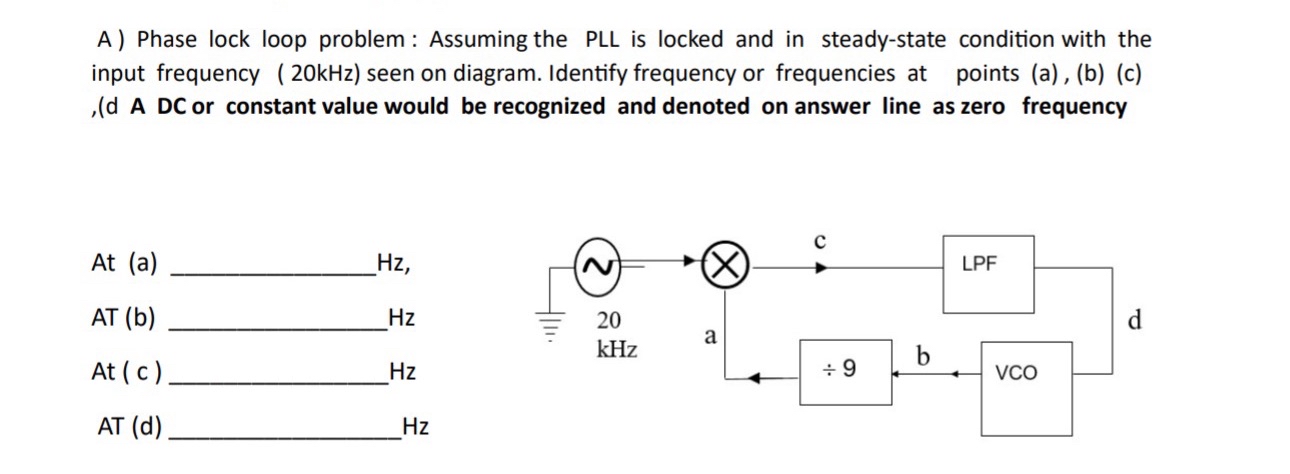

Question: A ) Phase lock loop problem: Assuming the PLL is locked and in steady - state condition with the input frequency ( 2 0 kHz

A Phase lock loop problem: Assuming the PLL is locked and in steadystate condition with the input frequency kHz seen on diagram. Identify frequency or frequencies at points abcd A DC or constant value would be recognized and denoted on answer line as zero frequency

At a

AT b

At c

AT d

Hz

Hz

A Phase lock loop problem: Assuming the PLL is locked and in steadystate condition with the input frequency kHz seen on diagram. Identify frequency or frequencies at points abcd A DC or constant value would be recognized and denoted on answer line as zero frequency

At a

AT b

At c

AT d

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock