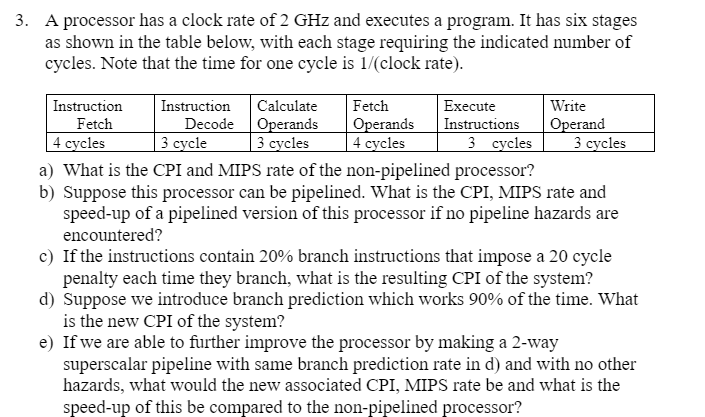

Question: A processor has a clock rate of 2 G H z and executes a program. It has six stages as shown in the table below,

A processor has a clock rate of and executes a program. It has six stages as shown in the table below, with each stage requiring the indicated number of cycles. Note that the time for one cycle is clock rate

a What is the CPI and MIPS rate of the nonpipelined processor?

b Suppose this processor can be pipelined. What is the CPI, MIPS rate and speedup of a pipelined version of this processor if no pipeline hazards are encountered?

c If the instructions contain branch instructions that impose a cycle penalty each time they branch, what is the resulting CPI of the system?

d Suppose we introduce branch prediction which works of the time. What is the new CPI of the system?

e If we are able to further improve the processor by making a way

superscalar pipeline with same branch prediction rate in d and with no other hazards, what would the new associated CPI, MIPS rate be and what is the speedup of this be compared to the nonpipelined processor?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock