Question: A software reference design has one main loop that takes 600 seconds to complete. The loop was executed on the target processor and each subroutine

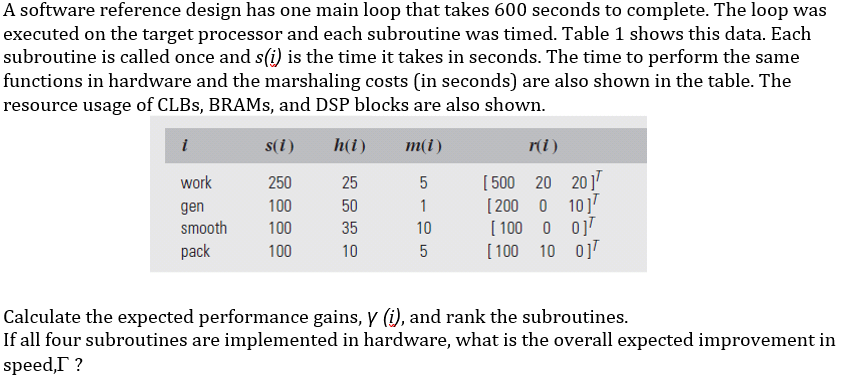

A software reference design has one main loop that takes 600 seconds to complete. The loop was executed on the target processor and each subroutine was timed. Table 1 shows this data. Eaclh subroutine is called once and s(i) is the time it takes in seconds. The time to perform the same functions in hardware and the marshaling costs (in seconds) are also shown in the table. The resource usage of CLBs, BRAMs, and DSP blocks are also shown work gen smooth pack 250 100 100 100 25 50 35 10 500 20 201 [200 0 10] 1100 0 0 100 10 01 10 Calculate the expected performance gains, (1), and rank the subroutines If all four subroutines are implemented in hardware, what is the overall expected improvement in speed, ? A software reference design has one main loop that takes 600 seconds to complete. The loop was executed on the target processor and each subroutine was timed. Table 1 shows this data. Eaclh subroutine is called once and s(i) is the time it takes in seconds. The time to perform the same functions in hardware and the marshaling costs (in seconds) are also shown in the table. The resource usage of CLBs, BRAMs, and DSP blocks are also shown work gen smooth pack 250 100 100 100 25 50 35 10 500 20 201 [200 0 10] 1100 0 0 100 10 01 10 Calculate the expected performance gains, (1), and rank the subroutines If all four subroutines are implemented in hardware, what is the overall expected improvement in speed

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts