Question: A solution with steps and guidance would be much appreciated. Thank you in advance o/ Problem 1: Calculate the minimum clock period for the pipelined

A solution with steps and guidance would be much appreciated. Thank you in advance o/

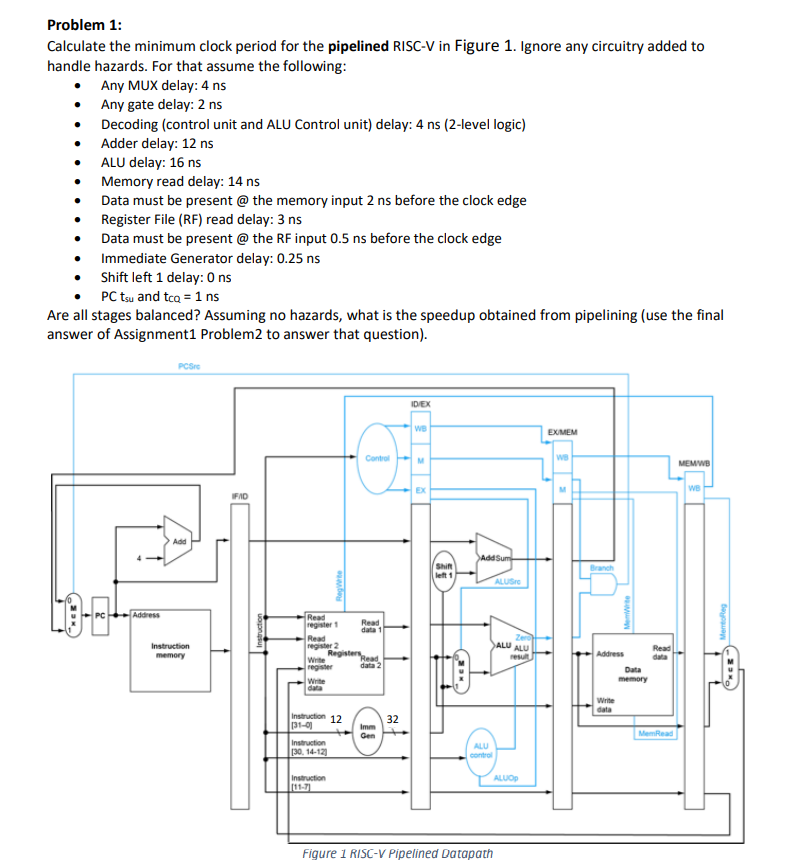

Problem 1: Calculate the minimum clock period for the pipelined RISC-V in Figure 1. Ignore any circuitry added to handle hazards. For that assume the following: Any MUX delay: 4 ns Any gate delay: 2 ns Decoding (control unit and ALU Control unit) delay: 4 ns (2-level logic) Adder delay: 12 ns ALU delay: 16 ns Memory read delay: 14 ns Data must be present @ the memory input 2 ns before the clock edge Register File (RF) read delay: 3 ns Data must be present @ the RF input 0.5 ns before the clock edge Immediate Generator delay: 0.25 ns Shift left 1 delay: Ons PC tsu and tco = 1 ns Are all stages balanced? Assuming no hazards, what is the speedup obtained from pipelining (use the final answer of Assignment1 Problem2 to answer that question). PCS IDEX WE EXMEM Control M WE MEMWE WE IFAD Add AddSum Shirt left 1 Branch Regte ALUS Lu- Address Read data 1 Mento Instruction memory ALU ALU Read register1 Read register 2 Write register Write data ageret Address Read dala data 2 memory Write data Instruction 12 32 31-01 Imm MemRead Instruction 30, 14-122 control Instruction ALUOP Figure 1 RISC-V Pipelined Datapath

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts