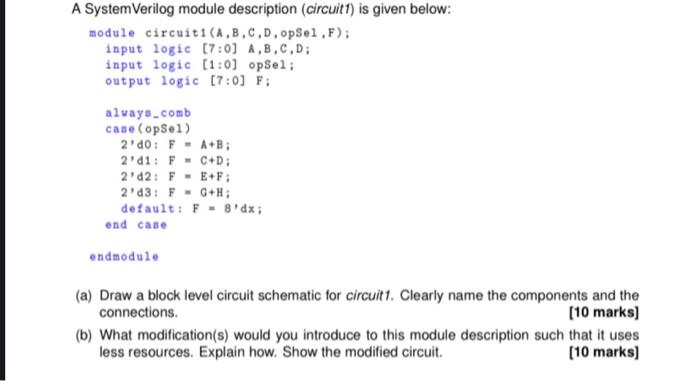

Question: A System Verilog module description (circuit 1) is given below: module circuiti (A,B,C,D,opel,F): input logic (7:0) A,B,C,D; input logic (1:0) opsel; output logic (7:0) F;

A System Verilog module description (circuit 1) is given below: module circuiti (A,B,C,D,opel,F): input logic (7:0) A,B,C,D; input logic (1:0) opsel; output logic (7:0) F; always.com case (opsel) 2'10: F - A+B; 2'01: F - C+D; 2'02: F - E+F; 2'03: F - G+H; default: F-8'dx; end case endmodule (a) Draw a block level circuit schematic for circuit1. Clearly name the components and the connections. [10 marks) (b) What modification(s) would you introduce to this module description such that it uses less resources. Explain how. Show the modified circuit. [10 marks)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts