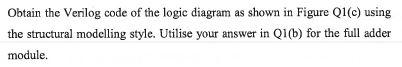

Question: a[3.2] b[3:21 a[1:0) b[1:0) 2 21 Coll 2 2 +C_in Fulladdr M1 Fulladde M2 C_out 2 Sum[3-2) 2 Sum[1:0) 1 1 2 Enable Adder_4 Y_out

![a[3.2] b[3:21 a[1:0) b[1:0) 2 21 Coll 2 2 +C_in Fulladdr](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f3bec5567ff_11766f3bec5064a6.jpg)

a[3.2] b[3:21 a[1:0) b[1:0) 2 21 Coll 2 2 +C_in Fulladdr M1 Fulladde M2 C_out 2 Sum[3-2) 2 Sum[1:0) 1 1 2 Enable Adder_4 Y_out Figure Q1(c) Obtain the Verilog code of the logic diagram as shown in Figure Q1(c) using the structural modelling style. Utilise your answer in Q1(b) for the full adder module. a[3.2] b[3:21 a[1:0) b[1:0) 2 21 Coll 2 2 +C_in Fulladdr M1 Fulladde M2 C_out 2 Sum[3-2) 2 Sum[1:0) 1 1 2 Enable Adder_4 Y_out Figure Q1(c) Obtain the Verilog code of the logic diagram as shown in Figure Q1(c) using the structural modelling style. Utilise your answer in Q1(b) for the full adder module

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts