Question: Adder Delay and Frequency. Assuming the adder delays from Exercise 1 , what is the fastest frequency at which you could reliably calculate a 6

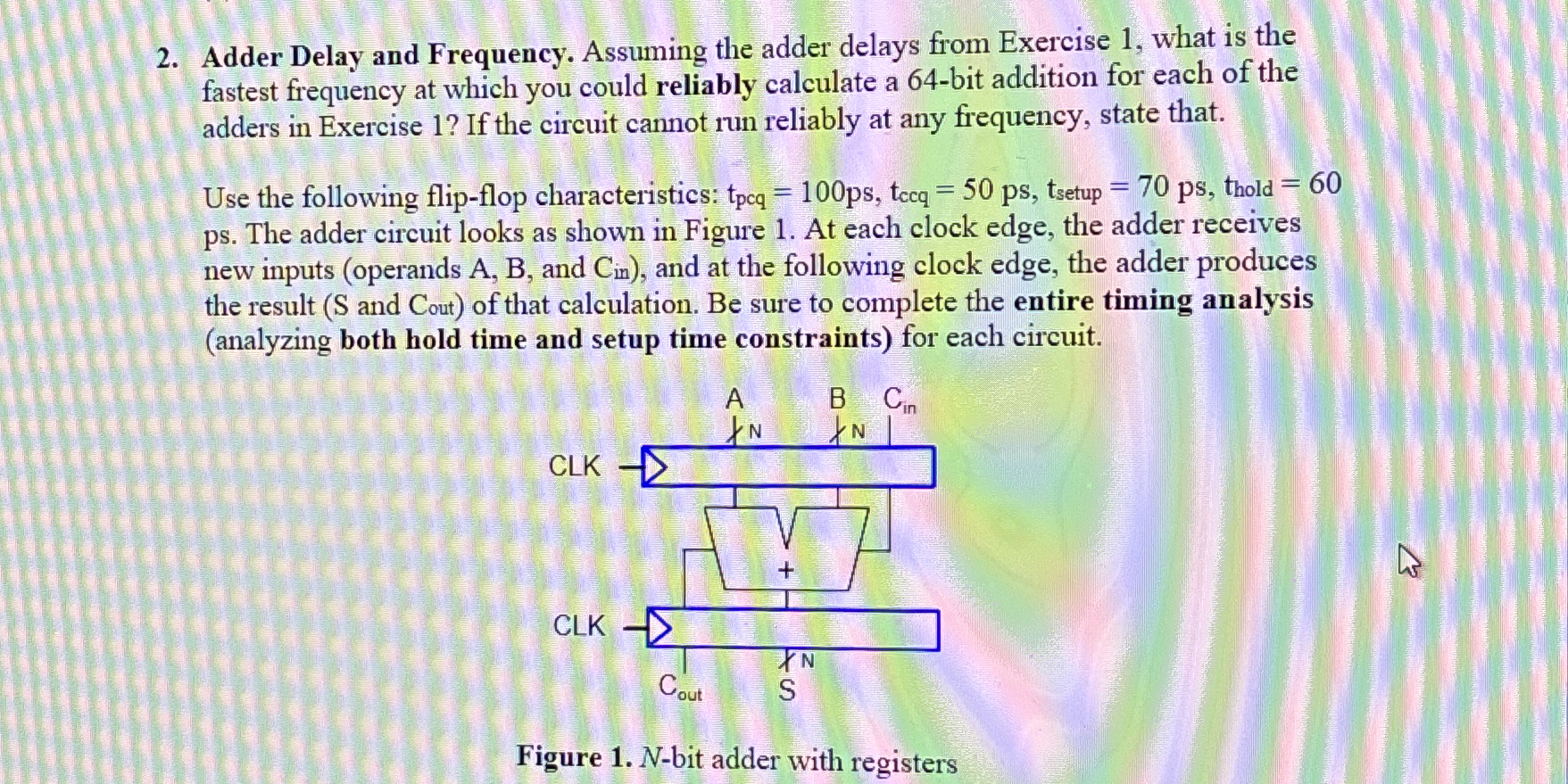

Adder Delay and Frequency. Assuming the adder delays from Exercise what is the fastest frequency at which you could reliably calculate a bit addition for each of the adders in Exercise If the circuit cannot run reliably at any frequency, state that.

Use the following flipflop characteristics: ps The adder circuit looks as shown in Figure At each clock edge, the adder receives new inputs operands and and at the following clock edge, the adder produces the result S and Cout of that calculation. Be sure to complete the entire timing analysis analyzing both hold time and setup time constraints for each circuit.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock