Question: An inverted page table can be used to further optimize space and time. How many PTEs are needed to store the page table? Assuming a

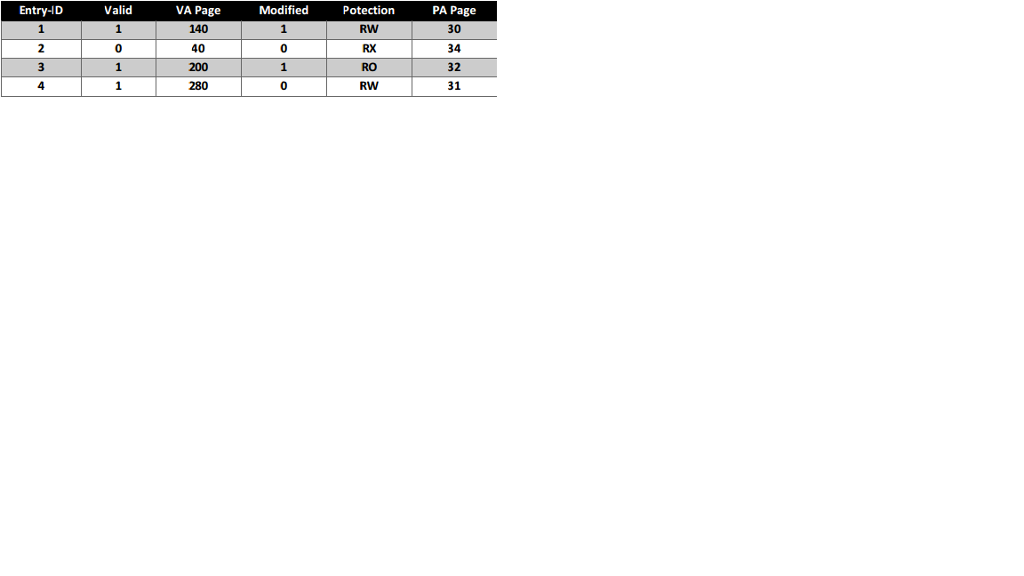

An inverted page table can be used to further optimize space and time. How many PTEs are needed to store the page table? Assuming a hash table implementation, what are the common case and worst case numbers of memory references needed for servicing a TLB miss? The following table shows the contents of a 4-entry TLB.

a) Under what scenarios would entry 2s valid bit be set to zero?

b) What happens when an instruction writes to VA page 30? When would a software managed TLB be faster than a hardware managed TLB?

c) What happens when an instruction writes to VA page 200?

Entry-ID Valid VA Page 140 40 2800 Modified Potection RW RO RW PA Page 34 31

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock