Question: Answer with good high level explanation please A processor has a 4 2 9 4 9 6 7 2 9 6 - byte data memory

Answer with good high level explanation please

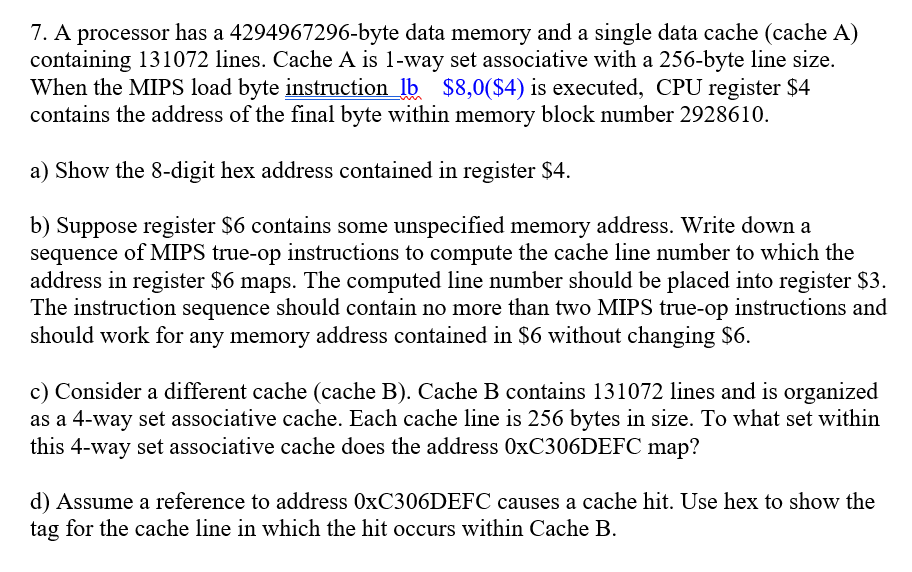

A processor has a byte data memory and a single data cache cache A

containing lines. Cache A is way set associative with a byte line size.

When the MIPS load byte instruction $$ is executed, CPU register $

contains the address of the final byte within memory block number

a Show the digit hex address contained in register $

b Suppose register $ contains some unspecified memory address. Write down a

sequence of MIPS trueop instructions to compute the cache line number to which the

address in register $ maps. The computed line number should be placed into register $

The instruction sequence should contain no more than two MIPS trueop instructions and

should work for any memory address contained in $ without changing $

c Consider a different cache cache B Cache B contains lines and is organized

as a way set associative cache. Each cache line is bytes in size. To what set within

this way set associative cache does the address xCDEFC map?

d Assume a reference to address DEFC causes a cache hit. Use hex to show the

tag for the cache line in which the hit occurs within Cache B

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock