Question: Assignment 2 Designing a Cache Simulato You should get a confirmation email once it is uploaded successfully. You will develop your cache simulator to operate

Assignment

Designing a Cache Simulato

You should get a confirmation email once it is uploaded successfully. You will develop your cache simulator to operate as with the cache memory we discussed in class and in your book. The cache will be configurable with following parameters:

Block size number of words. Note that we don't differentiate in this project for words and bytes. You can assume all addresses are referring to words, and no further byteword conversion is needed

You can assume all addresses are referring to word, needed Number of blocks in the cache. Associativity for direct, for twoway set associative Hit time in ycles

Your simulator should be able to handle direct mapped and way setassociative cache. You should use LRU least recently used replacement policy.

the testing guide Given this input and different configuration of your cache, compute the hit miss rate and the AMAT average memory access time You may hhoose reasonable values according to your need. Your program should also print out the final state of the cache using sett if applicable block# Valid bit and Tag.

Your cache only needs to support reads. You may choose CCPythonJavaMatlab as your preferred language. The testing guideline is provided below:

Testing guide: The e esting procedure makes sure that your program is working correctly. In the grading process we will evaluate with the following two steps:

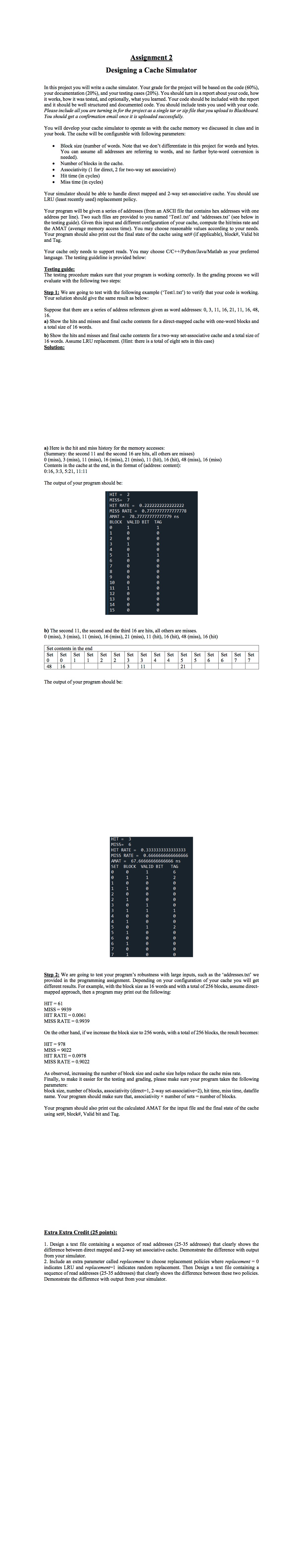

Step : We are going to test with the following example Testtxt to verify that your code is working. Your solution should give the same result as below:

Suppose that there are a series of address references given as word addresses: Show a Show

a Show the hits and miss a total size of words.

b Show the hits and misses and final cache contents for a twoway setassociative cache and a total size of words. sssume LRU replacement. Hint: there is a total of eight sets in this case Solution:

words. A Solution:

a Here is the hit and miss history for the memory accesses: Summary: the second and the second are hits, all others are missesmissmissmissmissmisshithitmissmiss Contents in the cache at the end, in the format of address: content:

:::: The output of your program should be:

b The second the second and the third are hits, all others are misses. missmissmissmissmisshithitmisshit

HTT MISS HIT RATE MISS RATE

On the other hand, if we increase the block size to words, with a total of blocks, the result becomes:

HIT MISS HIT RATE MISS RATE

Your program should also print out the using sett, block"t Valid bit and Tag.

Your program should also print out using sett, blockt, valid bit and Tas

Extra Extra Credit points

Designg a text file containing a sequence of read addresses addresses that clearly shows the difference between direct mapped and way set associtive cache. Demonostrate the difference with output

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock