Question: Assignment 2 Notes: Submission MUST be only 1 PDF or Doc format document of typed report. (For example, hand written scanned file is not acceptable.)

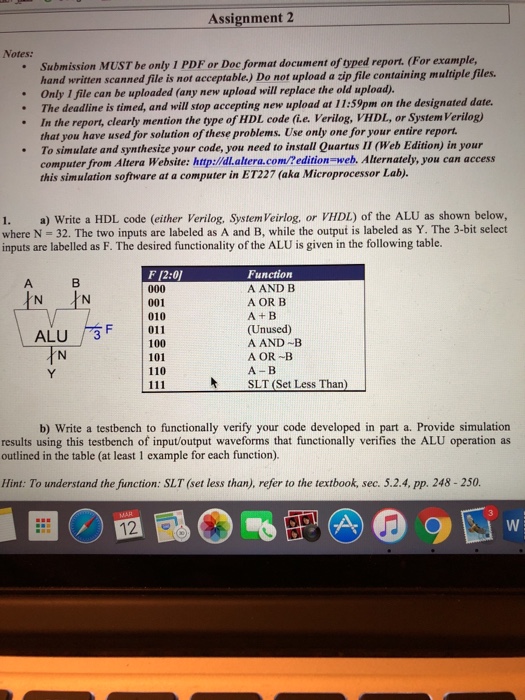

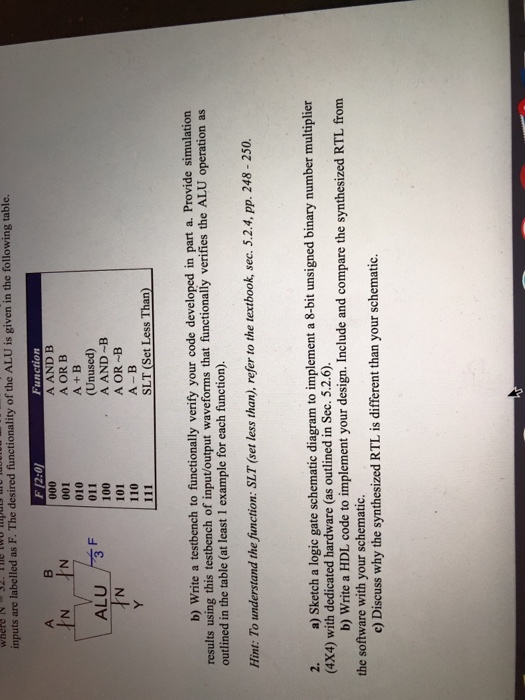

Assignment 2 Notes: Submission MUST be only 1 PDF or Doc format document of typed report. (For example, hand written scanned file is not acceptable.) Do not upload a zip file containing multiple files Only 1 file can be uploaded (any new upload will replace the old upload). The deadline is timed, and will stop accepting new upload at 11:59pm on the designated date. In the report, clearly mention the type of HDL code (ie. Verilog, VHDL, or System Verilog) that you have used for solution of these problems. Use only one for your entire report To simulate and synthesize your code, you need to install Quartus II (Web Edition) in your computer from Altera Website: http:lldl.altera.com/?edition web. Alternately, you can access this simulation software at a computer in ET227 (aka Microprocessor Lab). . 1. a) Write a HDL code (either Verilog, SystemVeirlog, or VHDL) of the ALU as shown below, where N = 32, The two inputs are labeled as A and B, while the output is labeled as Y. The 3-bit select inputs are labelled as F. The desired functionality of the ALU is given in the following table. Function A AND B A OR B A +B (Unused) A AND-B A OR B A-B SLT(Set Less Than) F [2:0 001 100 101 110 b) Write a testbench to functionally verify your code developed in part a. Provide simulation results using this testbench of input/output waveforms that functionally verifies the ALU operation as outlined in the table (at least 1 example for each function). Hint: To understand the function: SLT (set less than), refer to the textbook, sec. 5.2.4, pp. 248-250

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts