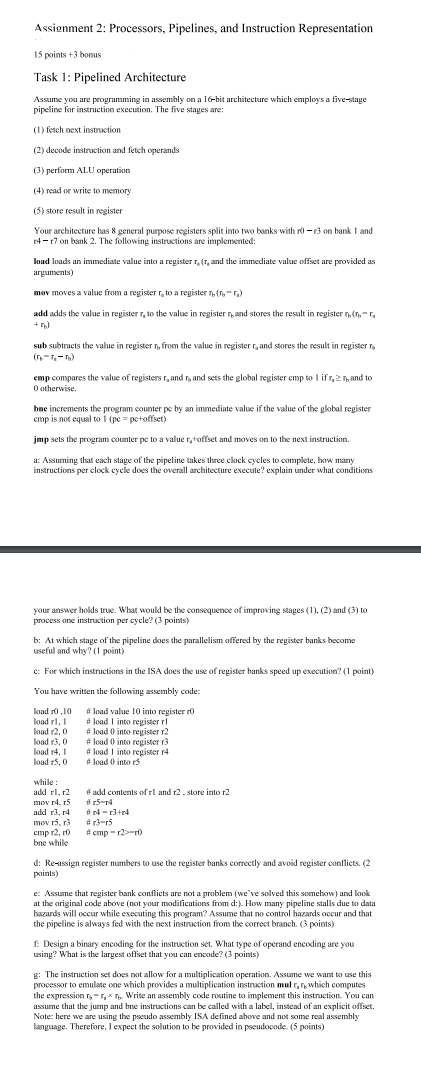

Question: Assignment 2 : Processors, Pipelines, and Instruction Representation 1 5 points + 3 bonus Task 1 : Pipelined Architecture Assume you are programming in assembly

Assignment : Processors, Pipelines, and Instruction Representation

points bonus

Task : Pipelined Architecture

Assume you are programming in assembly on a bit architecture which employs a fivestage pipeline for instruction execution. The five stages are:

fetch next instruction

decode instruction and fetch operands

perform ALU operation

read or write to memory

store result in register

Your architecture has general purpose registers split into two banks with rr on bank and mathrmrmathrmr on baink The following instructions are implemented:

load loads an immediate value into a register rb re and the immediate value offset are provided as arguments

mov moves a value from a register ra to a register rbleftrbraright

add adds the value in register ra to the value in register rb and stores the result in register rbleftrbrarightmathrmrmathrmb

sub subtracts the value in register rb from the value in register ra and stores the result in register rbleftrbrarbright

emp compares the value of registers ra and rb and sets the global register cmp to I if rgeq rb and to otherwise.

bae increments the program counter pe by an immediate value if the value of the global register cmp is not equal to mathrmpc petoffset

jmp sets the program counter pe to a value r toffset and moves on to the next instruction.

a: Assuming that each stage of the pipeline takes three clock cycles to complete, how many instructions per clock cycle does the overall architecture execute? explain under what conditions

your answer holds true. What would be the consequence of improving stages and to process one instruction per cycle? points

b: At which stage of the pipeline does the parallelism offered by the register banks become uscful and why? point

c: For which instructions in the ISA does the use of register banks speed up execution? point

You have written the following assembly code:

load r load value into register ro

load mathrmrlmathrmI# load into register rl

load r # load into register r

load r quad # load into register r

load mathrmrquad # load into register r

load rs# load into rs

while :

add mathrmrlmathrmrquad

otin add contents of rl and r store into r

mov r r ie rr

add mathrmrmathrmr if mathrmrmathrmrmathrmr

mov r r# mathrmrmathrmr

cmpr rquad # mathrmcmpmathrmrmathrmr

bne while

d: Reassign register numbers to use the register banks correctly and avoid register conflicts. points

e: Assume that register bank conflicts are not a problem weve solved this somehow and look at the original code above not your modifications from d: How many pipeline stalls due to data hazards will occur while executing this program? Assume that no control hazards occur and that the pipeline is always fed with the next instruction from the correct branch. points

f Design a binary encoding for the instruction set. What type of operand encoding are you using? What is the largest offset that you can encode? points

g: The instruction set does not allow for a multiplication operation. Assume we want to use this processor to emulate one which provides a multiplication instruction mul ra rb which computes the expression rrtimes rb Write an assembly code routine to implement this instruction. You can assume that the jump and boe instructions can be called with a label, instead of an explicit offect. Note: here we are using the pseudo assembly ISA defined above and not some real assembly language. Therefore, I expect the solution to be provided in pseudocode. points

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock