Question: Assume that for a program compiled for the MIPS instruction set, 25% of all instructions are loads and stores. Of these, 60% were performed

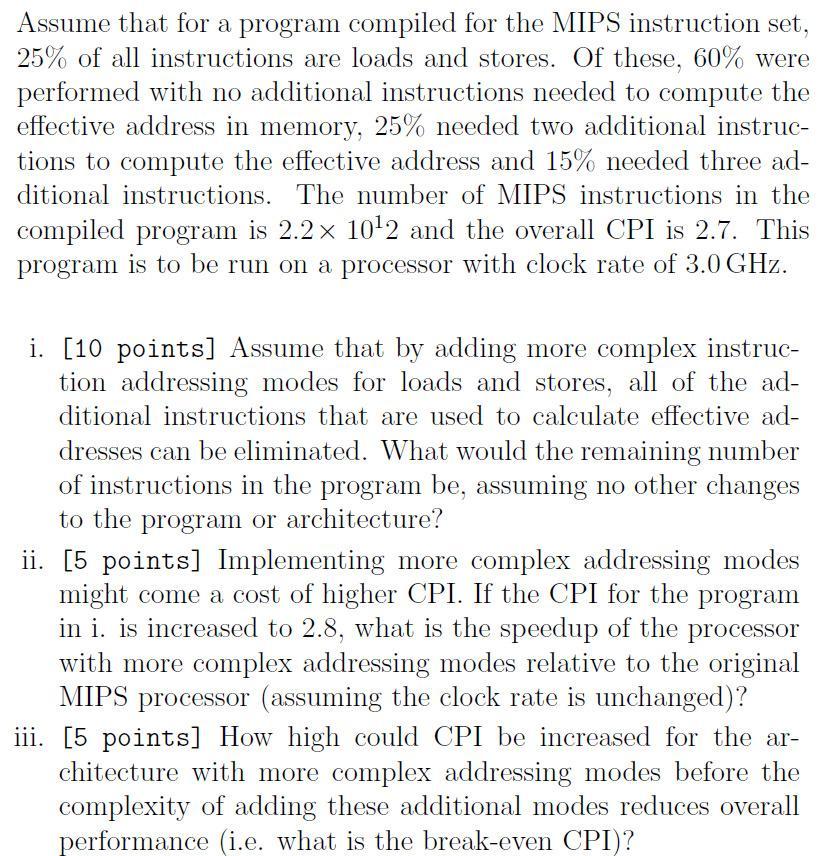

Assume that for a program compiled for the MIPS instruction set, 25% of all instructions are loads and stores. Of these, 60% were performed with no additional instructions needed to compute the effective address in memory, 25% needed two additional instruc- tions to compute the effective address and 15% needed three ad- ditional instructions. The number of MIPS instructions in the compiled program is 2.2 102 and the overall CPI is 2.7. This program is to be run on a processor with clock rate of 3.0 GHz. i. [10 points] Assume that by adding more complex instruc- tion addressing modes for loads and stores, all of the ad- ditional instructions that are used to calculate effective ad- dresses can be eliminated. What would the remaining number of instructions in the program be, assuming no other changes to the program or architecture? ii. [5 points] Implementing more complex addressing modes might come a cost of higher CPI. If the CPI for the program in i. is increased to 2.8, what is the speedup of the processor with more complex addressing modes relative to the original MIPS processor (assuming the clock rate is unchanged)? iii. [5 points] How high could CPI be increased for the ar- chitecture with more complex addressing modes before the complexity of adding these additional modes reduces overall performance (i.e. what is the break-even CPI)?

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts