Question: Assume the following: . The memory is byte addressable. . Memory accesses are to 1-byte words (not to 4-byte words). . . Addresses are 10

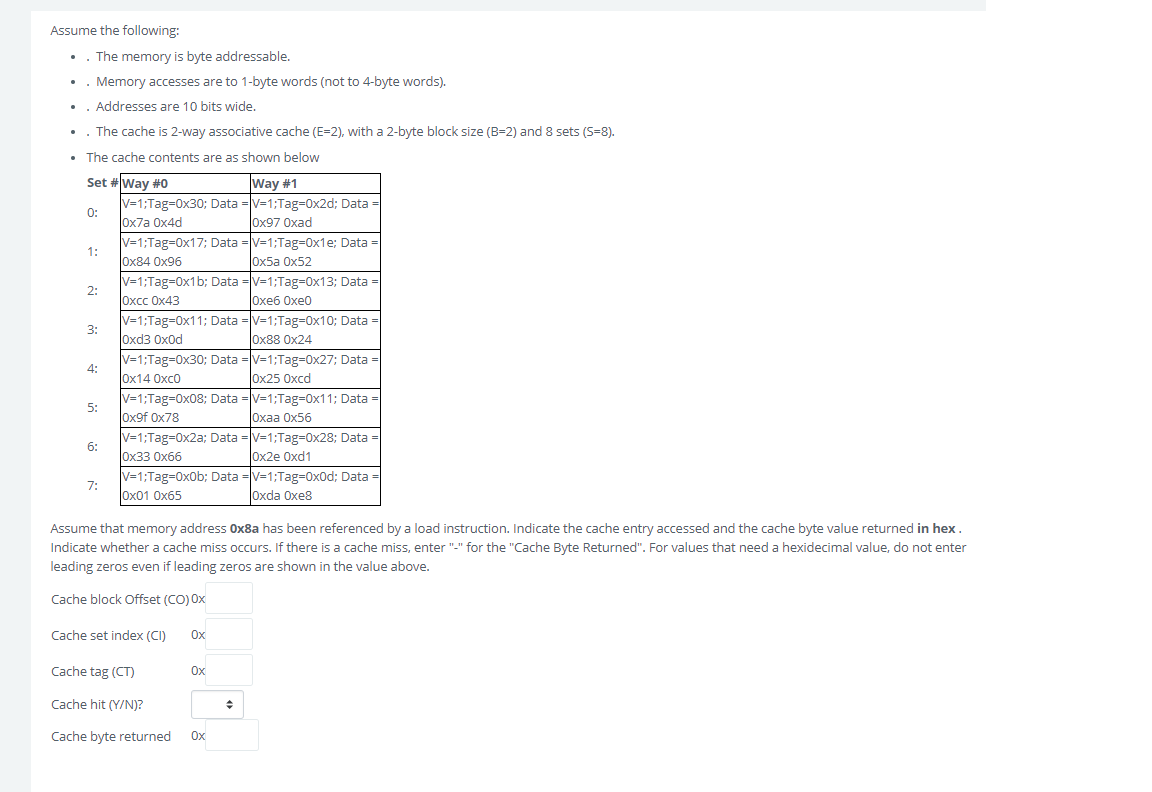

Assume the following: . The memory is byte addressable. . Memory accesses are to 1-byte words (not to 4-byte words). . . Addresses are 10 bits wide. .. The cache is 2-way associative cache (E=2), with a 2-byte block size (B=2) and 8 sets (S=8). The cache contents are as shown below Set #Way #0 Way #1 v=1;Tag=0x30; Data = v=1;Tag=0x2d; Data = 0: Ox7a Ox4d Ox97 Oxad V=1;Tag=0x17; Data = v=1;Tag=0x1e; Data = 1: Ox84 0x96 Ox5a Ox52 V=1;Tag=0x1b; Data = v=1;Tag=0x13; Data = 2: Oxcc Ox43 Oxe6 Oxeo V=1;Tag=0x11; Data = v=1;Tag=0x10; Data = 3: Oxd3 OxOd Ox88 0x24 V=1;Tag=0x30; Data = v=1;Tag=0x27; Data = 4: Ox14 Oxco Ox25 Oxcd V=1;Tag=0x08; Data = v=1;Tag=0x11; Data = 5: Ox9f Ox78 Oxaa Ox56 V=1;Tag=0x2a; Data = v=1;Tag=0x28; Data = 6: 0x33 0x66 Ox2e Oxd1 V=1;Tag=0x0b; Data - V=1;Tag=0xOd; Data = 7: Ox01 0x65 Oxda Oxe8 Assume that memory address 0x8a has been referenced by a load instruction. Indicate the cache entry accessed and the cache byte value returned in hex. Indicate whether a cache miss occurs. If there is a cache miss, enter "-" for the "Cache Byte Returned". For values that need a hexidecimal value, do not enter leading zeros even if leading zeros are shown in the value above. Cache block Offset (CO) Ox Cache set index (CI) Ox Cache tag (CT) Cache hit (Y/N)? Cache byte returned Ox

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts