Question: (b) (10 points) Complete the VHDL architecture below for the unsigned 12-bit Adder_Subtracter using behavioral style VHDL. The mode signal when 'o makes an adder,

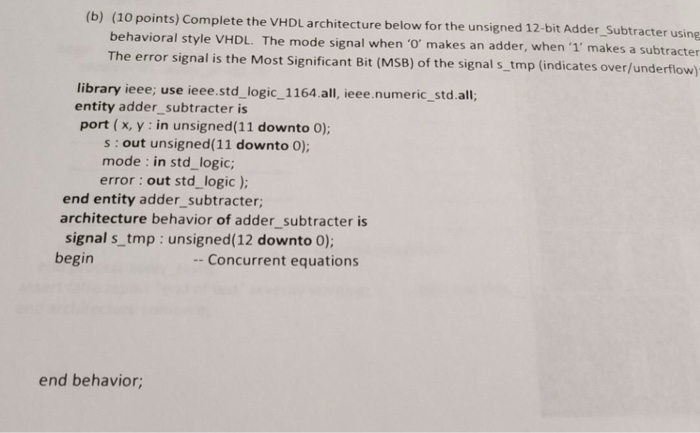

(b) (10 points) Complete the VHDL architecture below for the unsigned 12-bit Adder_Subtracter using behavioral style VHDL. The mode signal when 'o makes an adder, when 1 makes a subtracter The error signal is the Most Significant Bit (MSB) of the signal s tmp (indicates over/underflow)y library ieee; use ieee.std_logic_1164.all, ieee.numeric_std.all entity adder_subtracter is port (x, y: in unsigned(11 downto O); s: out unsigned(11 downto 0); mode : in std_logic; error: out std_logic ); end entity adder_ subtracter; architecture behavior of adder_subtracter is signal s tmp: unsigned(12 downto O); begin Concurrent equations end behavior

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts