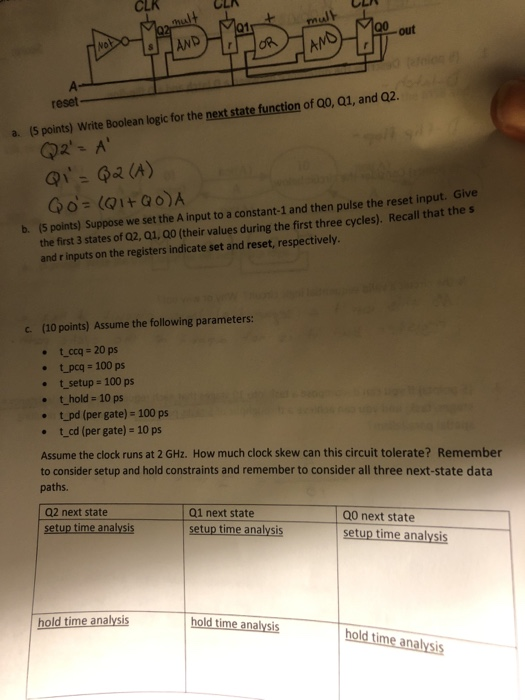

Question: B & c CLK out reset a. (S points) Write Boolean logic for the next state function of 00, Q1, and Q2. Q2- A the

B & c

B & c CLK out reset a. (S points) Write Boolean logic for the next state function of 00, Q1, and Q2. Q2- A the first 3 states of Q2, Q1, Q0 (their values during the first three cycles). Recall that the s and r inputs on the registers indicate set and reset, respectively. b. (5 points) Suppose we set the A input to a constant-1 and then pulse the reset input. Give c. (10 points) Assume the following parameters: t_ccq # 20 ps t_pcq 100 ps e t setup 100 ps t hold 10 ps e t pd (per gate) 100 ps . t_cd (per gate) 10 ps Assume the clock runs at 2 GHz. How much clock skew can this circuit tolerate? Remember to consider setup and hold constraints and remember to consider all three next-state data paths. Q2 next state setup time analysis Q1 next state setup time analysis Q0 next state setup time analysis hold time analysis hold time analysis hold time analysis CLK out reset a. (S points) Write Boolean logic for the next state function of 00, Q1, and Q2. Q2- A the first 3 states of Q2, Q1, Q0 (their values during the first three cycles). Recall that the s and r inputs on the registers indicate set and reset, respectively. b. (5 points) Suppose we set the A input to a constant-1 and then pulse the reset input. Give c. (10 points) Assume the following parameters: t_ccq # 20 ps t_pcq 100 ps e t setup 100 ps t hold 10 ps e t pd (per gate) 100 ps . t_cd (per gate) 10 ps Assume the clock runs at 2 GHz. How much clock skew can this circuit tolerate? Remember to consider setup and hold constraints and remember to consider all three next-state data paths. Q2 next state setup time analysis Q1 next state setup time analysis Q0 next state setup time analysis hold time analysis hold time analysis hold time analysis

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts