Question: Bijan's pipelined processor features separate instruction and data caches. The instruction cache (I-cache) has a single level and the data cache (D-cache) has two

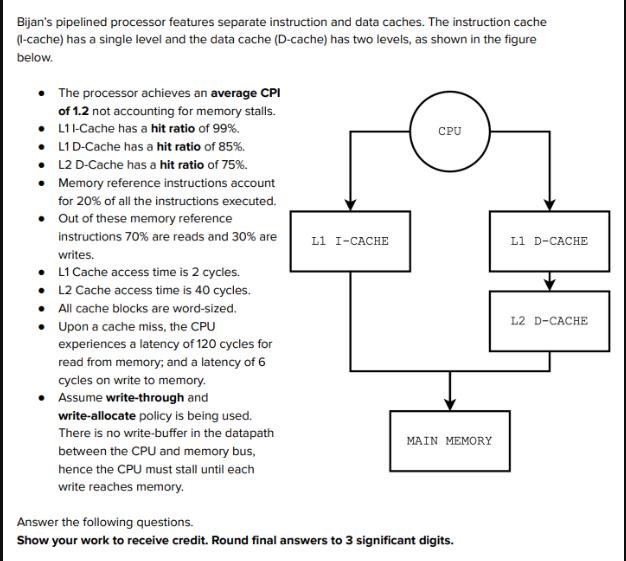

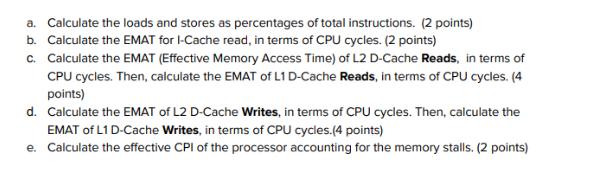

Bijan's pipelined processor features separate instruction and data caches. The instruction cache (I-cache) has a single level and the data cache (D-cache) has two levels, as shown in the figure below. The processor achieves an average CPI of 1.2 not accounting for memory stalls. L1 I-Cache has a hit ratio of 99%. L1D-Cache has a hit ratio of 85%. L2 D-Cache has a hit ratio of 75%. Memory reference instructions account for 20% of all the instructions executed. Out of these memory reference instructions 70% are reads and 30% are writes. L1 Cache access time is 2 cycles. L2 Cache access time is 40 cycles. All cache blocks are word-sized. Upon a cache miss, the CPU experiences a latency of 120 cycles for read from memory; and a latency of 6 cycles on write to memory. Assume write-through and write-allocate policy is being used. There is no write-buffer in the datapath between the CPU and memory bus, hence the CPU must stall until each write reaches memory. Answer the following questions. L1 I-CACHE L1 D-CACHE MAIN MEMORY Show your work to receive credit. Round final answers to 3 significant digits. L2 D-CACHE a. Calculate the loads and stores as percentages of total instructions. (2 points) b. Calculate the EMAT for I-Cache read, in terms of CPU cycles. (2 points) c. Calculate the EMAT (Effective Memory Access Time) of L2 D-Cache Reads, in terms of CPU cycles. Then, calculate the EMAT of L1 D-Cache Reads, in terms of CPU cycles. (4 points) d. Calculate the EMAT of L2 D-Cache Writes, in terms of CPU cycles. Then, calculate the EMAT of L1 D-Cache Writes, in terms of CPU cycles.(4 points) e. Calculate the effective CPI of the processor accounting for the memory stalls. (2 points)

Step by Step Solution

There are 3 Steps involved in it

To answer these questions well need to work through each part stepbystep Lets begin a Calculate the loads and stores as percentages of total instructions Given that memory reference instructions accou... View full answer

Get step-by-step solutions from verified subject matter experts