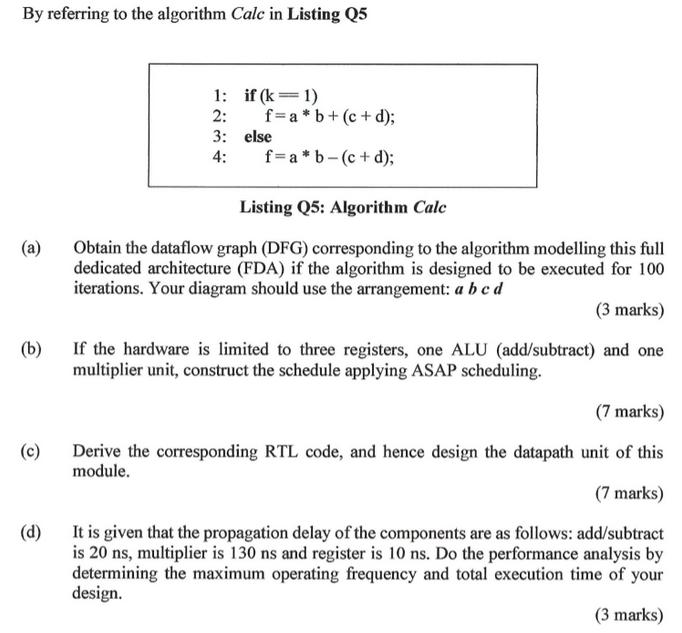

Question: By referring to the algorithm Calc in Listing Q5 (a) 1: 2: 3: 4: if (k-1) (c) f=a*b+(c + d); else Listing Q5: Algorithm

By referring to the algorithm Calc in Listing Q5 (a) 1: 2: 3: 4: if (k-1) (c) f=a*b+(c + d); else Listing Q5: Algorithm Calc Obtain the dataflow graph (DFG) corresponding to the algorithm modelling this full dedicated architecture (FDA) if the algorithm is designed to be executed for 100 iterations. Your diagram should use the arrangement: a b cd (3 marks) (b) If the hardware is limited to three registers, one ALU (add/subtract) and one multiplier unit, construct the schedule applying ASAP scheduling. f=a* b-(c+d); (7 marks) Derive the corresponding RTL code, and hence design the datapath unit of this module. (7 marks) (d) It is given that the propagation delay of the components are as follows: add/subtract is 20 ns, multiplier is 130 ns and register is 10 ns. Do the performance analysis by determining the maximum operating frequency and total execution time of your design. (3 marks)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts