Question: bytes (32-bit processor), and 16 lines (64 bytes) of cache with this machine. : FHow 24 bit address is divided into tag, line number and

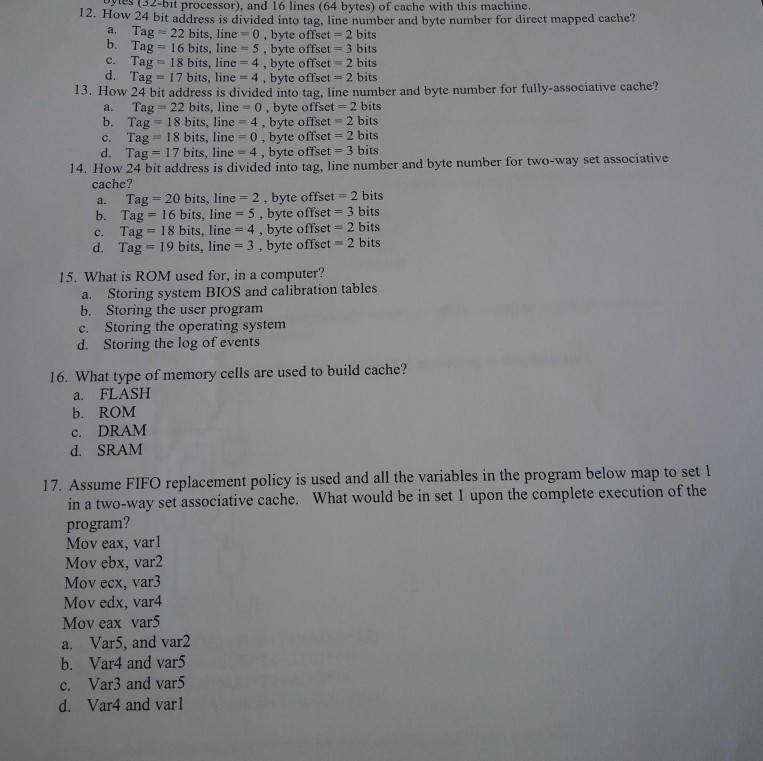

bytes (32-bit processor), and 16 lines (64 bytes) of cache with this machine. : FHow 24 bit address is divided into tag, line number and byte number for direct mapped cache? a. Tag 22 bits, line 0, byte offset 2 bits b. Tag 16 bits, line 5, byte offset 3 bits c. Tag 18 bits, line 4, byte offset 2 bits d. Tag 17 bits, line 4, byte offset-2 bits 13. How 24 bit address is divided into tag, line number and byte number for fully-associative cache? a. Tag 22 bits, line - 0, byte offset 2 bits b. Tag 18 bits, line 4, byte offset - 2 bits c. Tag 18 bits, line 0, byte offset- 2 bits d. Tag 17 bits, line- 4, byte offset 3 bits 14. How 24 bit address is divided into tag, line number and byte number for two-way set associative cache? a. Tag 20 bits, line 2, byte offset 2 bits b. Tag 16 bits, line 5, byte offset 3 bits c. Tag 18 bits, line 4, byte offset 2 bits d. Tag 19 bits, line 3, byte offset 2 bits 15. What is ROM used for, in a computer? Storing system BIOS and calibration tables a. b. Storing the user program c. Storing the operating system d. Storing the log of events 16. What type of memory cells are used to build cache? a. FLASH b. ROM c. DRAM d. SRAM 17. Assume FIFO replacement policy is used and all the variables in the program below map to set 1 et associative cache. What would be in set 1 upon the complete execution of the program? Mov eax, varl Mov ebx, var2 Mov ecx, var3 Mov edx, var4 Mov eax var5 a. Var5, and var2 b. Var4 and var5 c. Var3 and var5 d. Var4 and varl

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts