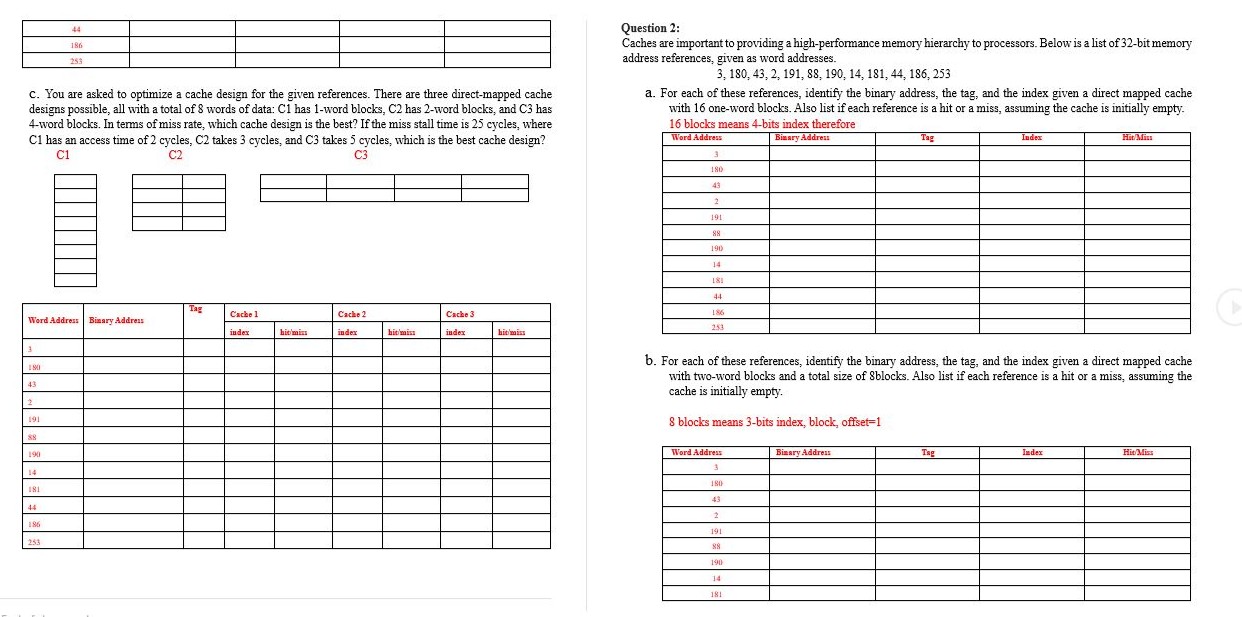

Question: c . You are asked to optimize a cache design for the given references. There are three direct - mapped cache designs possible, all with

c You are asked to optimize a cache design for the given references. There are three directmapped cache

designs possible, all with a total of words of data: has word blocks, has word blocks, and has

word blocks. In terms of miss rate, which cache design is the best? If the miss stall time is cycles, where

has an access time of cycles, takes cycles, and takes cycles, which is the best cache design?

C

Question :

Caches are important to providing a highperformance memory hierarchy to processors. Below is a list of bit memory

address references, given as word addresses.

a For each of these references, identify the binary address, the tag, and the index given a direct mapped cache

with oneword blocks. Also list if each reference is a hit or a miss, assuming the cache is initially empty.

blocks means bits index therefore

b For each of these references, identify the binary address, the tag, and the index given a direct mapped cache

with twoword blocks and a total size of Sblocks. Also list if each reference is a hit or a miss, assuming the

cache is initially empty.

blocks means bits index, block, offset

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock