Question: Cache block size (B) can affect both miss rate and miss latency. Assuming a machine with a base CPI of 1, and an average

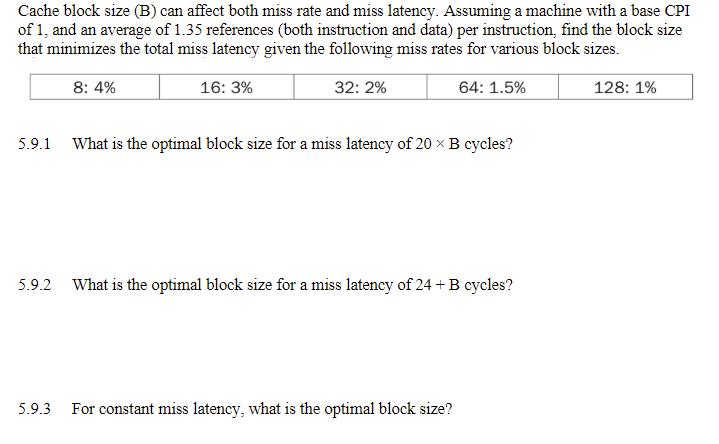

Cache block size (B) can affect both miss rate and miss latency. Assuming a machine with a base CPI of 1, and an average of 1.35 references (both instruction and data) per instruction, find the block size that minimizes the total miss latency given the following miss rates for various block sizes. 8: 4% 16: 3% 32: 2% 5.9.1 5.9.2 64: 1.5% What is the optimal block size for a miss latency of 20 B cycles? What is the optimal block size for a miss latency of 24+ B cycles? 5.9.3 For constant miss latency, what is the optimal block size? 128: 1%

Step by Step Solution

There are 3 Steps involved in it

Block Size In bytes Miss Rate In 8 4 16 3 32 2 a Optimal block size for latency of 20 B cycl... View full answer

Get step-by-step solutions from verified subject matter experts