Question: Can someone please help with this code? I am not understanding why I am getting these outcomes in the Behavioral Simulation using Vivado program. The

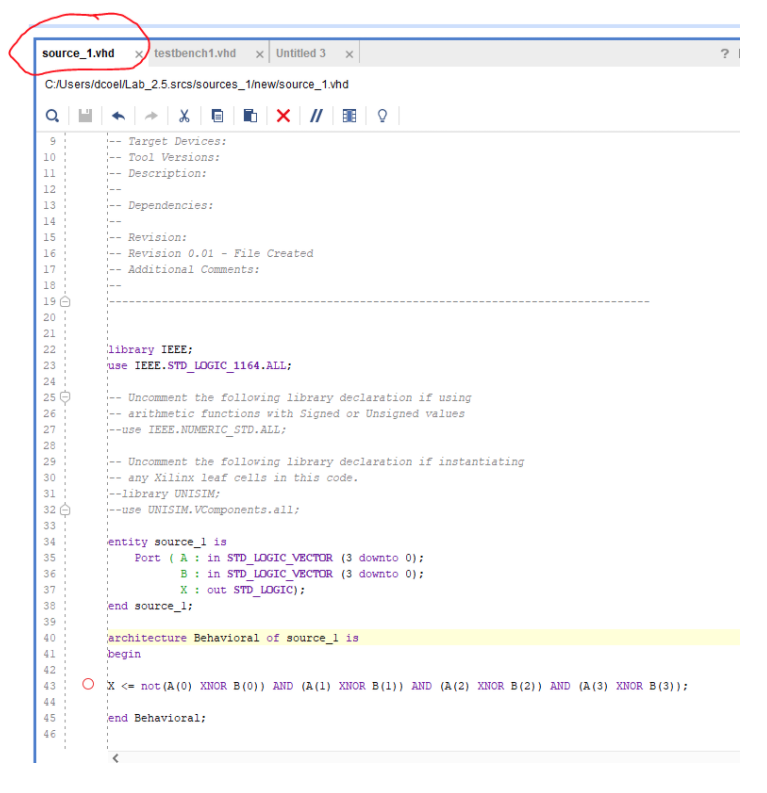

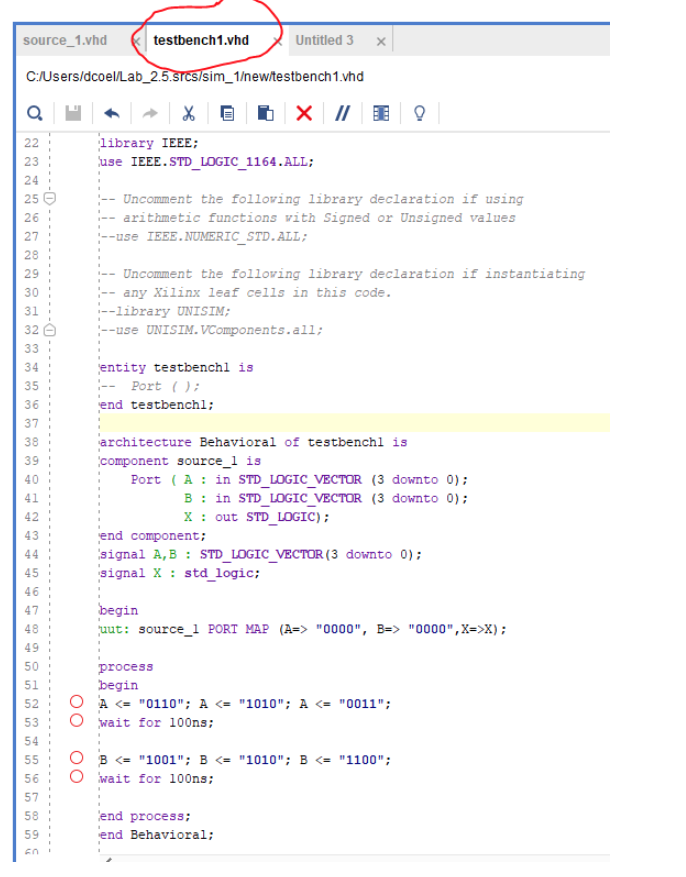

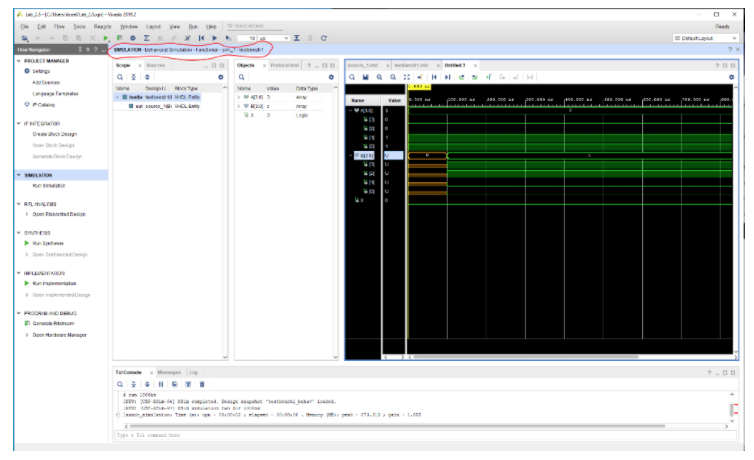

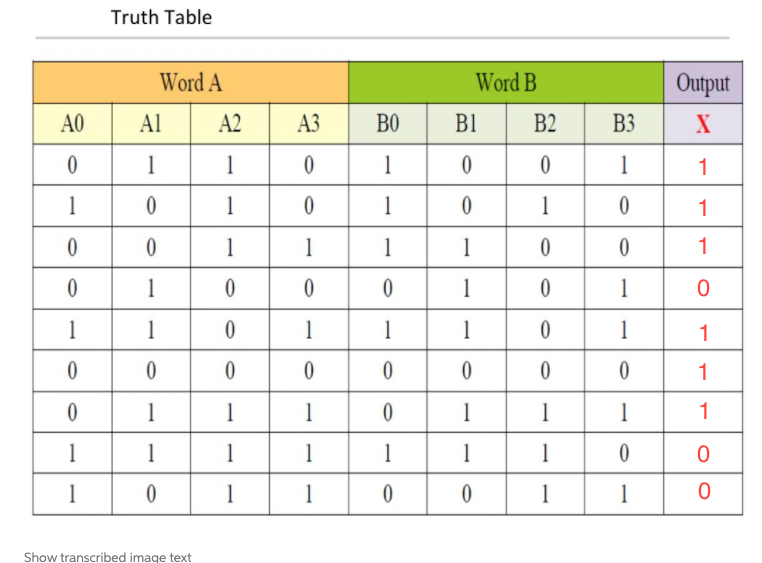

Can someone please help with this code? I am not understanding why I am getting these outcomes in the Behavioral Simulation using Vivado program. The U and C and X signal seem to be wrong and I cant find the problem. Along with A having a 3. I have provided my source/testbech/behavioral simulation in order. The last picture (truth table) is the output X that is needed to be for the values. Can you please show me how to code this in Vivado using the format "std_logic_vector"?

source_1.vhd testbench 1.vhd x Untitled 3 C:/Users/dcoel/Lab_2.5.srcs/sources_1ew/source_1.vhd o Target Devices: Tool Versions: Description: Dependencies: Revision: Revision 0.01 - File Created Additional Comments: library IEEE; use IEEE. STD_LOGIC_1164.ALL; 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 Uncomment the following library declaration if using arithmetic functions with Signed or Unsigned values --use IEEE. NUMERIC_STD. ALL; Uncomment the folloving library declaration if instantiating any Xilinx leaf cells in this code. --library UNISIM; --use UNISIM. VComponents.all; D entity source_1 is Port (A in STD_LOGIC_VECTOR (3 downto 0); B: in STD_LOGIC_VECTOR (3 downto 0); X : out STD_LOGIC); end source_1; architecture Behavioral of source_1 is begin O x "0000", B=> "0000",X=>x); 50 51 process begin O A "0000", B=> "0000",X=>x); 50 51 process begin O A

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts