Question: Can you help solve my errors Homewo Overview In this assignment modules will be completed that compute a 2 s + b > c where

Can you help solve my errors

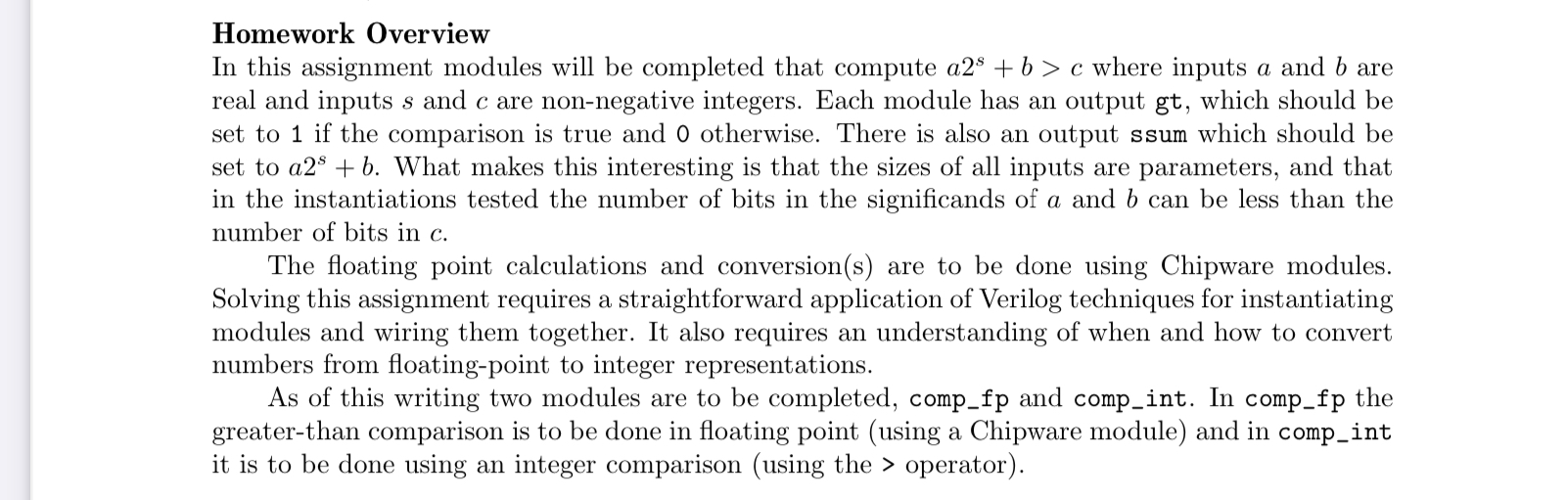

Homewo Overview

In this assignment modules will be completed that compute where inputs a and are

real and inputs and are nonnegative integers. Each module has an output gt which should be

set to if the comparison is true and otherwise. There is also an output ssum which should be

set to What makes this interesting is that the sizes of all inputs are parameters, and that

in the instantiations tested the number of bits in the significands of a and can be less than the

number of bits in

The floating point calculations and conversions are to be done using Chipware modules.

Solving this assignment requires a straightforward application of Verilog techniques for instantiating

modules and wiring them together. It also requires an understanding of when and how to convert

numbers from floatingpoint to integer representations.

As of this writing two modules are to be completed, compfp and compint. In compfp the

greaterthan comparison is to be done in floating point using a Chipware module and in compint

it is to be done using an integer comparison using the operator file: actual: Fri Oct ::

: hwv

assign ssum shiftedexp, asig bsig;

xmvlog: EEXPRPA hwv: expecting a right parenthesis IEEE

assign ssum shiftedexp, asig bsig;

l

xmvlog: EMISEXX hwv: expecting an or sign in an assignment IEEE

assign ssum shiftedexp, asig bsig;

l

xmvlog: EEXPSMC hwv: expecting a semicolon ;IEEE

module worklib.compfp:v

errors: warnings:

compfp #wcwcwswswexpwexpwsigwsigwsigwsig

xmvlog: EEXPLPA hwv: expecting a left parenthesis AMSLRM

sumssum

xmvlog: EEXPRPAhwv: expecting a right parenthesis IEEE

gt

xmvlog: EEXPLPA hwv: expecting a left parenthesis IEEE

aa

l

xmvlog: EEXPLPA hwv: expecting a left parenthesis IEEE

bb

xmvlog: EEXPLPA hwv: expecting a left parenthesis IEEE

ss

l

xmvlog: EEXPLPA hwv: expecting a left parenthesis IEEE

cc

xmvlog: EEXPLPA hwv: expecting a left parenthesis IEEE

;

xmvlog: EEXPLPA hwv: expecting a left parenthesis IEEE

module worklib.compint:v

errors: warnings:

xrun: EVLGERR: An error occurred during parsing. Review the log file for errors with the code E and fix those identified problems to proceed. Exiting

swith code status

TOOL: : Exiting Oct ::: ::

Problem

Complete scaledcompfp so the comparison is done in FP

Use Chipware modules for floatingpoint operations and conversions.

Make sure that the testbench does not report errors.

Module must be synthesizable. Use command: genus files syntcl

Don't assume any particular parameter values.

Code must be written clearly.

typedef enum logic :

Rndtoeven Rndto Rndtoplusinf

Rndtominusinf Rndtonearup Rndfrom

Rnd;

module compfp

int wfp wexp wsig, wfp wexp wsig

output logic gt

output logic wfp: ssum,

input uwire wfp: a b

input uwire ws: s

input uwire wc: c;

logic wsig: asig, bsig;

logic wexp: aexp, bexp;

assign asig awsig:wsigwsigb;

assign bsig bwsig:wsigwsigb;

assign aexp awfp:wsig;

logic wexp: shiftedexp;

assign shiftedexp aexp s;

assign ssum shiftedexp, asig bsig;

Convert a and b to FP values with wsigbit significands.

Compute a s

Compute ssum as b;

Compute gt a s b c;

The greaterthan comparison must be done as FP comparison.

assign ssum ;

assign gt ;

assign gt ssum cb : b;

endmodule Problem

Complete scaledcompint so the comparison is done as an int.

I Use Chipware modules for floatingpoint operations and conversions.

I Make sure that the testbench does not report errors.

Module must be synthesizable. Use command: genus files syntcl

Don't assume any particular parameter values.

Code must be written clearly.

module compint

# int wc ws wexp wsig

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock