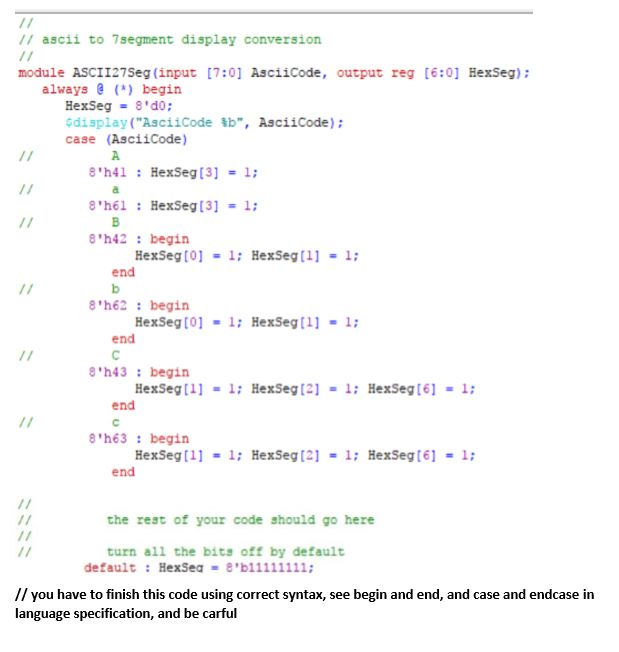

Question: Can you please find the errors in the syntax? and provide a structure that compiles. Its supposed to be a VERILOG code that converts ascii

Can you please find the errors in the syntax? and provide a structure that compiles. Its supposed to be a VERILOG code that converts ascii hex to 7segment display. Thank you

/ ascii to 7segment display conversion module ASCII27Seg (input [7:01 Asciicode, output reg [6:0] HexSeg) always() begin ?display ("Ascicode case (AsciiCode) ", Ascicode); 8"h41 : Hexseg [3] 1; = 8'h42 begin end 8'h62 begin end 8'h43begin HexSeg[1-1: HexSeg[-1: HexSegt61-1 end 8'h63: begin HexSeg [1] = 1; HexSeg[2] = 1; HexSeg [6] 1; = end the rest of your code should go here turn all the bits off by default // you have to finish this code using correct syntax, see begin and end, and case and endcase in language specification, and be carful

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts