Question: Chat GPT answers will be reported . AI software will be reported . Do not copy answers from elsewhere, work manually. In Verilog, implement a

Chat GPT answers will be reported. AI software will be reported. Do not copy answers from elsewhere, work manually.

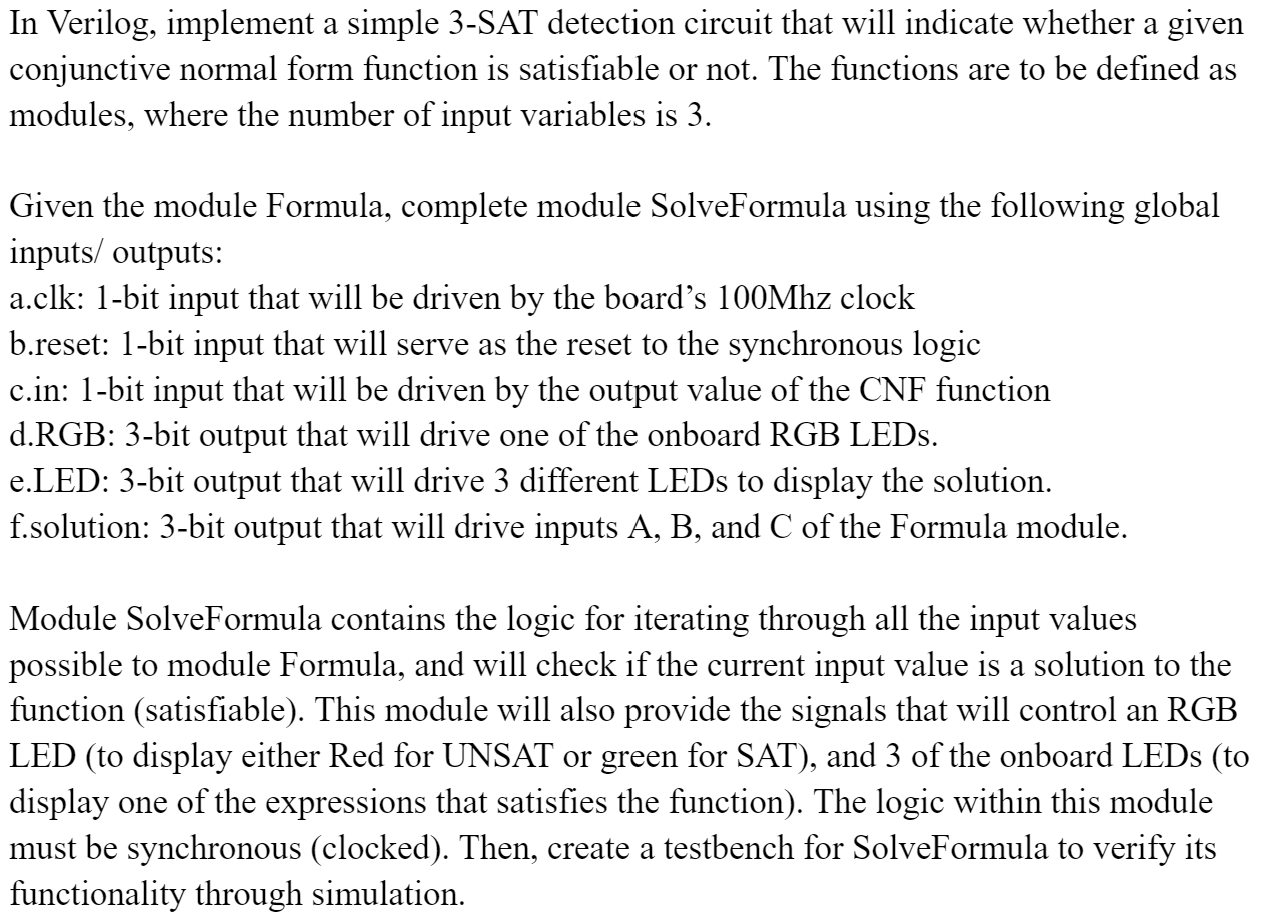

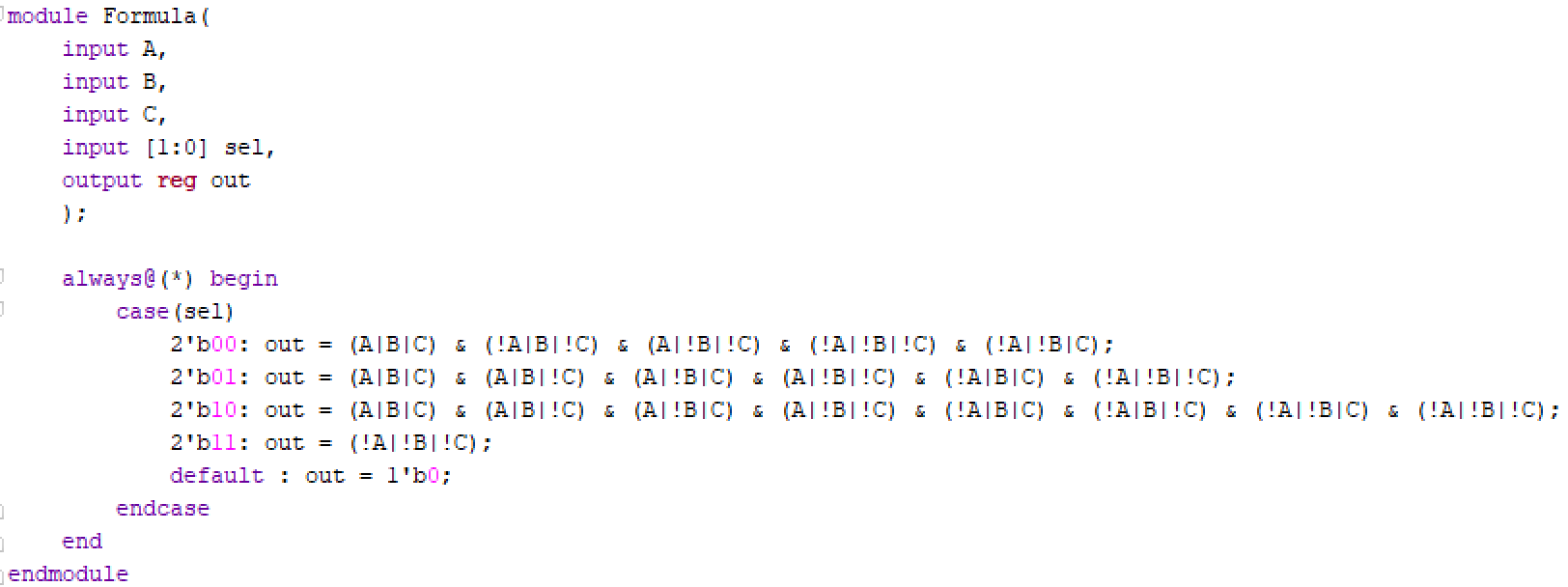

In Verilog, implement a simple 3-SAT detection circuit that will indicate whether a given conjunctive normal form function is satisfiable or not. The functions are to be defined as modules, where the number of input variables is 3 . Given the module Formula, complete module SolveFormula using the following global inputs/ outputs: a.clk: 1-bit input that will be driven by the board's 100Mhz clock b.reset: 1-bit input that will serve as the reset to the synchronous logic c.in: 1-bit input that will be driven by the output value of the CNF function d.RGB: 3-bit output that will drive one of the onboard RGB LEDs. e.LED: 3-bit output that will drive 3 different LEDs to display the solution. f.solution: 3-bit output that will drive inputs A, B, and C of the Formula module. Module SolveFormula contains the logic for iterating through all the input values possible to module Formula, and will check if the current input value is a solution to the function (satisfiable). This module will also provide the signals that will control an RGB LED (to display either Red for UNSAT or green for SAT), and 3 of the onboard LEDs (to display one of the expressions that satisfies the function). The logic within this module must be synchronous (clocked). Then, create a testbench for SolveFormula to verify its functionality through simulation. In Verilog, implement a simple 3-SAT detection circuit that will indicate whether a given conjunctive normal form function is satisfiable or not. The functions are to be defined as modules, where the number of input variables is 3 . Given the module Formula, complete module SolveFormula using the following global inputs/ outputs: a.clk: 1-bit input that will be driven by the board's 100Mhz clock b.reset: 1-bit input that will serve as the reset to the synchronous logic c.in: 1-bit input that will be driven by the output value of the CNF function d.RGB: 3-bit output that will drive one of the onboard RGB LEDs. e.LED: 3-bit output that will drive 3 different LEDs to display the solution. f.solution: 3-bit output that will drive inputs A, B, and C of the Formula module. Module SolveFormula contains the logic for iterating through all the input values possible to module Formula, and will check if the current input value is a solution to the function (satisfiable). This module will also provide the signals that will control an RGB LED (to display either Red for UNSAT or green for SAT), and 3 of the onboard LEDs (to display one of the expressions that satisfies the function). The logic within this module must be synchronous (clocked). Then, create a testbench for SolveFormula to verify its functionality through simulation

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts